本原创文章由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注明出处

一、FSK信号的解调原理

FSK信号的解调也有非相干和相干两种,FSK信号可以看作是用两个频率源交替传输得到的,所以FSK的接收机由两个并联的ASK接收机组成。

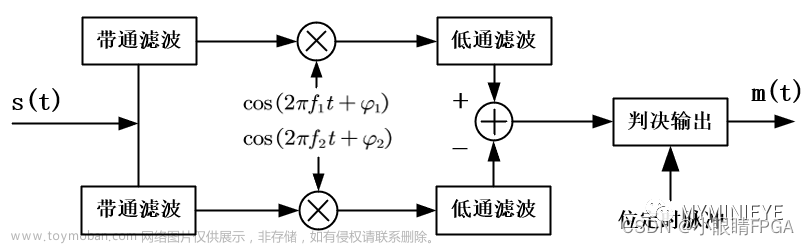

(1)相干解调

相干解调是利用乘法器,输入一路与载频相干的参考信号与载频相乘,通过低通滤波,滤除高频信号,即得原始信号,FSK经过带通滤波之后,可以看作是两路ASK信号,相干检测器组成的原理如下所示:

FSK相干解调结构

上图是一种易于实现的FSK相干解调器,还有一种最佳FSK相干解调器如下所示:

FSK最佳解调结构

从图上可以看出,在接收端要产生两个已知信号s1(t)和s2(t)的波形,分别和输入波形相乘,再送往积分器,在一定时间内积分,在t=Tb时刻,将积分结果取样,并在比较器中比较判决,然后输出,整个相干解调器的性能受载波锁相环路以及位同步性能影响很大,并且在高速率的情况下,积分、取样和清洗电路难以实现,因此通常采用第一种相干解调器的结构。

(2)非相干解调

由于FSK信号中提取相干载波相对比较困难,实际工程应用中多用非相干解调法,在相同误码率的条件下,非相干解调需要的信噪比只比相干解调高1~2dB。非相干解调的种类有很多,例如:基于自适应滤波的解调法、差分检波算法、AFC环解调法、过零检测法、包络检波法等。

• 基于自适应滤波的解调法

在自适应解调中,较常见的方法是利用自适应滤波器中的单一频率的自适应陷波器进行解调,它能提供易于控制的带宽和及其深的零点,具有自适应地跟踪载波的频率和相位的能力,它等效于有一个复权的自适应滤波器,用两个实权同时调整单一频率正弦波的幅度和相位,以跟踪原始输入信号的幅度和相位,消除干扰。如下是自适应滤波器的结构:

自适应滤波结构

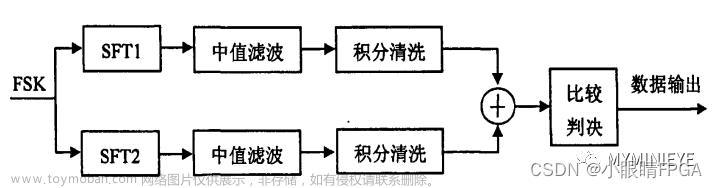

自适应滤波中的单频跟踪技术应用于解调时,兼有解调和锁相的功能,选取适当的步长可以达到较小的传输延迟,并获得优良的解调性能。二进制FSK信号有两个调制频率,能量主要集中在这两个频率。分别采用两个自适应滤波(SFT)跟踪这两个频率的信号,即可将键控频率分量提取出来。然后经过中值滤波提取包络、积分清洗、抽样判决即可还原基带信号。比最佳非相干解调拥有更好的误码性能,特别适合低速率数据场合,解调系统示意图如下:

自适应解调FSK原理

• 差分检波算法

差分检波法解调FSK的原理如下所示:

差分检波法解调原理

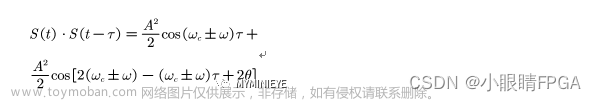

设带通滤波器的输出为:

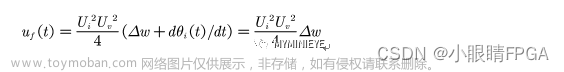

其中We为载波频率,w是角频率偏移,为初始相位,则乘法器的输出为:

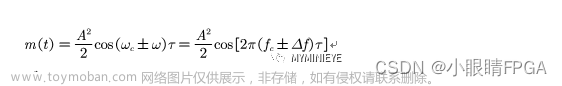

用低通滤波器滤除倍频分量,可以得到

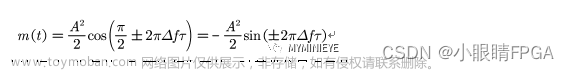

如果令,则

当FSK取上边频时,为负值,取下边频为正值,随基带信号码元的不同,低通滤波输出正负变化的正弦波,通过抽样判决,即可实现FSK信号的解调。这种方法结构上相 对简单,计算量小,便于实现。

• AFC环解调法

AFC环是一个负反馈系统,如果接收信号与本振存在频差,则在一定时间内必然存在相差,鉴相器输出的相位误差信号微分后,得到反映频差的误差信号,经过平滑处理, 控制VCO的震荡频率向输入信号频率靠近最终使得频差近似为零。应用比较广泛的是相乘微分型AFC环路,结构如下所示:

相乘微分型解调原理

设输入信号为:

VCO输入信号为:

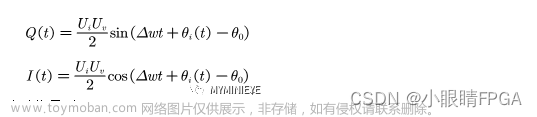

由上图可知:

输入信号为单载波信号时:

因此 反映了输入信号和VCO输出信号的频差,对FSK信号来讲,

反映了输入信号和VCO输出信号的频差,对FSK信号来讲,  即为调制信号,对其进行滤波判决,即可完成FSK信号的解调。AFC环是根据信号的瞬时频 率来解调数据的,当FSK调制度较小时,区分调制数据越困难,解调性能也越差。

即为调制信号,对其进行滤波判决,即可完成FSK信号的解调。AFC环是根据信号的瞬时频 率来解调数据的,当FSK调制度较小时,区分调制数据越困难,解调性能也越差。

• 过零检测法

过零检测法是一种常用且简便的解调方法,2FSK信号的过零点数随载频的变化而 不同,因此检测出过零点个数就可以得到载频的差异,从而进一步得到调制信号的信息,过零检测法的原理如下:

过零检测法解调原理

FSK信号经过限幅、微分、整流后形成与频率变化相对应的脉冲序列,由此再形成 相同宽度的矩形脉冲,矩形脉冲的低频分量与数字信号相对应,由滤波器滤出低频分量, 然后经抽样判决,即可得到原始的数字调制信号。

• 包络检波法

2FSK的包络检波法解调原理如下,可视为由两路2ASK解调电路组成,这里两个带通滤波器,对应两个中心频率,用以分开两路2ASK信号,将两路滤波之后的包络信号相减,在经过抽样判决其进行判决,根据调制规则(f1代表符号1,f2代表符号0),当判决值大于0时,判决为1,否则判决为0。

包络检波法解调原理

包络检波首先需要通过带通滤波器将FSK信号进行滤波分离,显然,当调制度较小的时候,两路FSK信号频谱混叠严重,带通滤波器的通带比较窄,能量损失比较严重,会引入另一路信号的频谱干扰,因此性能下降严重,通常需要调制度大于2的时候才能获得较好测性能。

二、FSK解调技术的matlab仿真

这里采用AFC环来实现FSK的解调,之所以选择AFC环是因为AFC环是基于锁相环路的解调技术,且环路增益计算相对简单,可以初步学习锁相环的相关知识。AFC环中有3个滤波器,其中两个正交之路的低通滤波完全相同,用于滤除前级混频后的高频分量;环路滤波器用于滤除鉴频器输出产生的高频分量,产生NCO的控制信号。为了简化设计,环路滤波器也设计成FIR低通滤波器,这样可以直接从环路滤波器的输出信号中获取解调数据,环路滤波器的带宽,过渡带可以和混频器的低通滤波器保持一致。

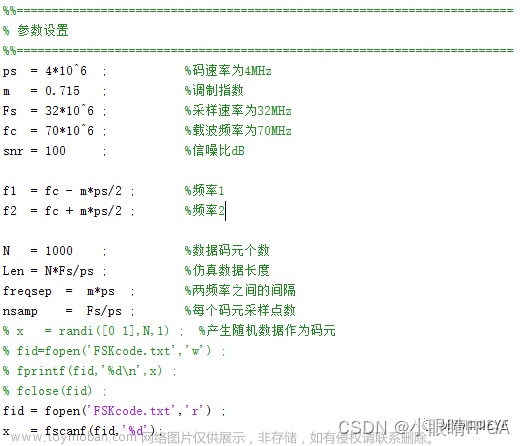

FSK调制信号的参数如下,其中码元速率为4MHz,采样频率为32MHz,载波频率为70MHz,调制指数为0.715。码元为随机产生的数据,需要写入本地,作为后续比对的数据。

通过fskmod函数产生调制信号,然后将基带信号变频到70MHz的中频,叠加一定的信道噪声,再使用抗混叠滤波器滤除带外频率,防止输入信号的最大频率与采样频率冲突。

然后把数据写入文本作为FPGA解调的输入数据。

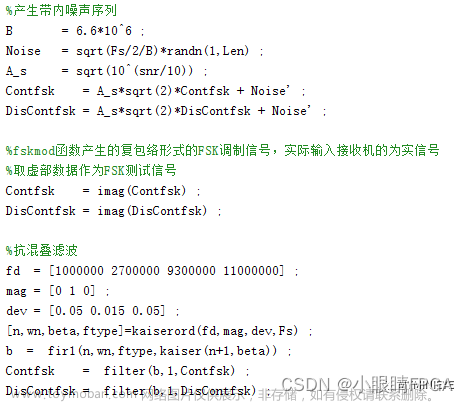

设计低通滤波器,滤波器通带及过渡带的选择有一个基本的原则,就是确保有用信号完全通过,尽可能多地对噪声及干扰进行滤除。低通滤波器的通带必须大于捕获带宽,捕获带宽也就是锁相环路起始的频差,为确保不损失有用信号信息,这里选择3.6MHz。

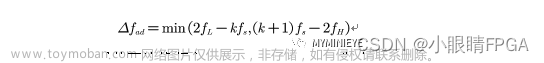

理论上讲,截止频率越靠近通带频率越好,但是过渡带越窄,滤波器的阶数就越多,所需的硬件资源也越多。过渡带带宽的选择原则有两个:一是必须确保滤除相邻的A/D镜像频率成分;二是需要滤除数字下变频引入的倍频分量。根据带通采样定理,A/D镜像频率的最小间隔为:

式中fL为中频信号的下边缘频率(70-3.6=66.4MHz),fH为中频信号的上边缘频率(70+3.6=73.6MHz),fs为采样频率(32MHz),k为整数,易求得

数字下变频引入的倍频分量最低频率为:

式中,f0为中频采样后的载波频率(6MHz),也可以在频谱中看到,Bf为中频信号处理带宽(7.2MHz),m为整数,易求得fcddc = 8.4MHz。

滤波器的设计如下:

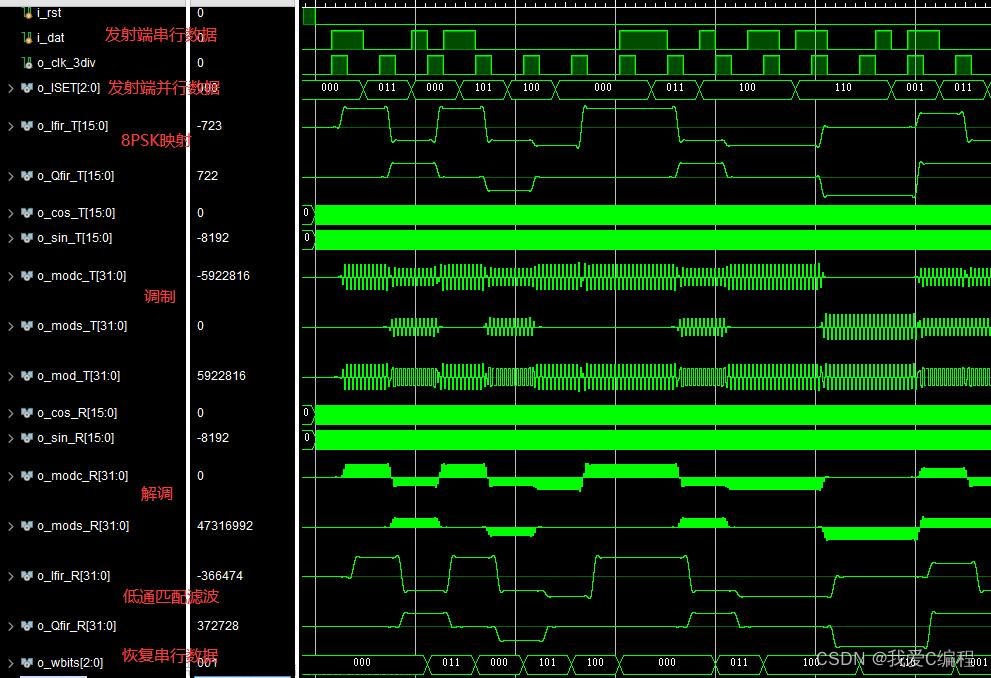

三、FSK解调技术的FPGA实现

AFC环中滤波器设计可以直接导入matlab参数,但是采用FPGA进行数学意义上的微分运算时分困难,根据微分运算的规则,我们可以采用一种简单的近似处理方法,即通过求取前后两个数据之差来代替微分运算,前后两个数据间隔为一个时钟周期

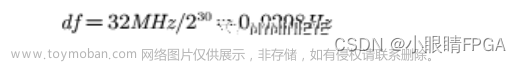

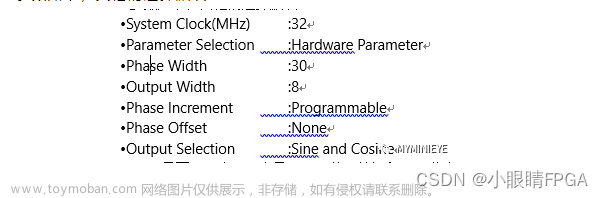

采用前后两个数据之差来代替微分运算,相当于数学上的微分运算乘以时钟速率这个常数,反映在AFC环路上,相当于环路增益乘了一个常数。NCO的参数设计比较简单,区董事中频率选择系统时钟即可,为32MHz,频率字位宽选取30bit,数据位宽为8bit,NCO频率分辨率为

环路锁定的条件是环路增益K必须大于固有频差,且环路增益越大,捕获及锁定时间越短。对2FSK信号,可以设置本地NCO的初始频率为载波频率fc,固有频差即为FSK信号的频偏值,当调制指数为0.715时,码元速率为4MHz,

因此环路能够稳定跟踪FSK信号的变化,解调出原始数据。

1.DDS参数如下,其他的选择默认:

2.Multiplier需要用两个,一个是8*8bit的,数据和DDS位宽都是8位的,取低15位作为有效输出数据。另一个是18*18的,考虑到FPGA中集成硬件乘法器IP核大多多事18*18bit的,DSP48E1是18*25,如果超过18位就需要用两个DSP了,占用更多资源,因此在微分之后取高18位做乘法运算,采用有符号乘法器即可。

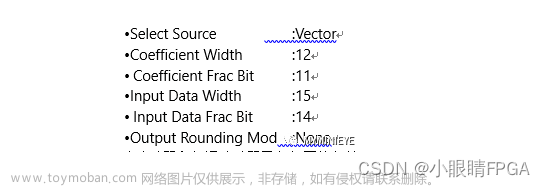

3.低通滤波器导入matlab产生的系数,参数设置如下,其他的选择默认:

4.环路滤波器和低通滤波器导入相同的参数,输入数据的位宽可以根据自己截位的舍取进行选择,这里使用的17位,即微分之后,取高17位作为有效数据,然后输入环路滤波器。

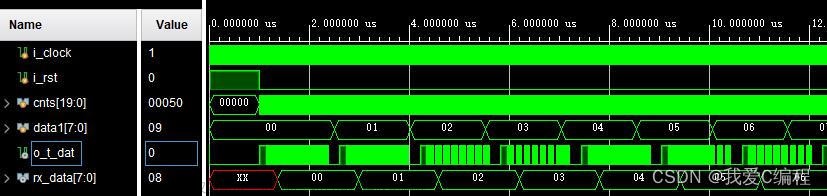

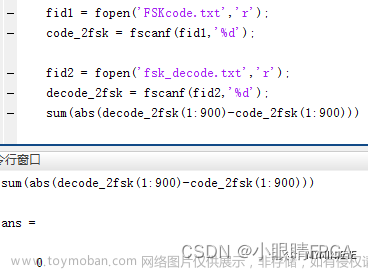

编写测试文件,环路滤波器输出的数据即为FSK解调信号,然后通过抽样判决,位同步时钟提取,即可得到二进制码元,把解调的数据写入到本地,用于数据比对。

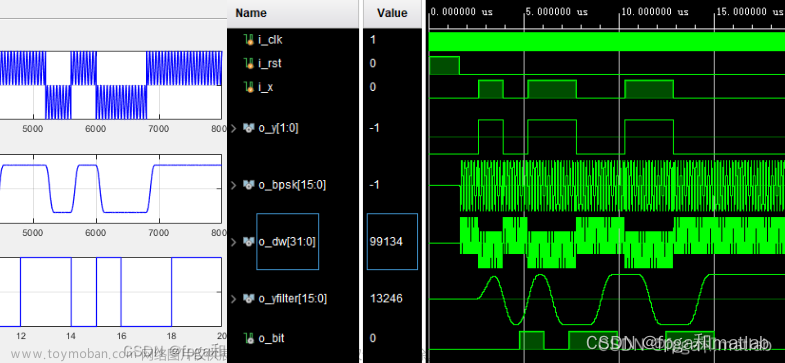

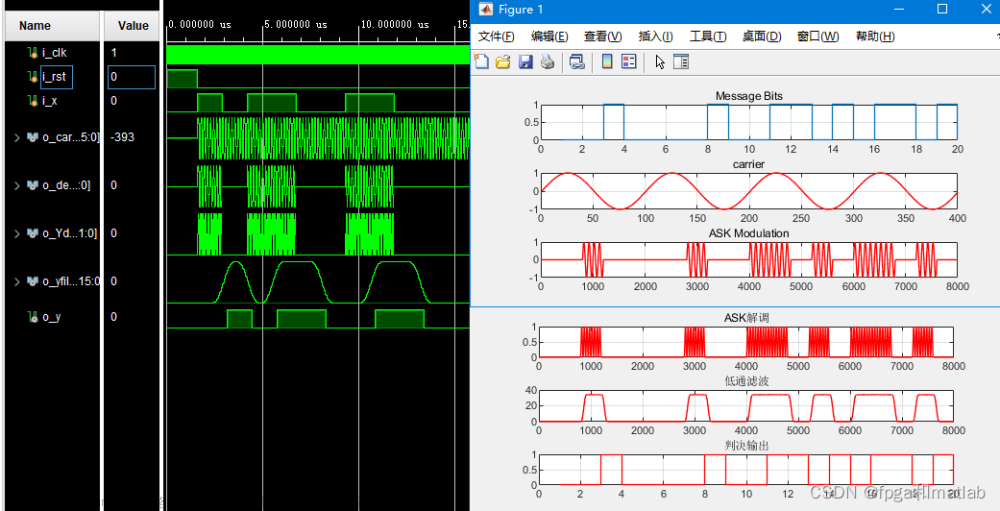

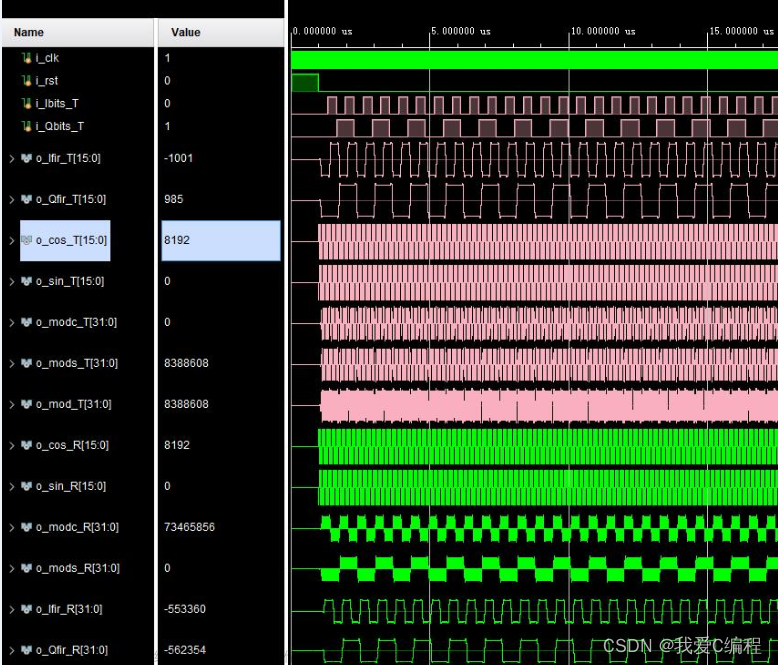

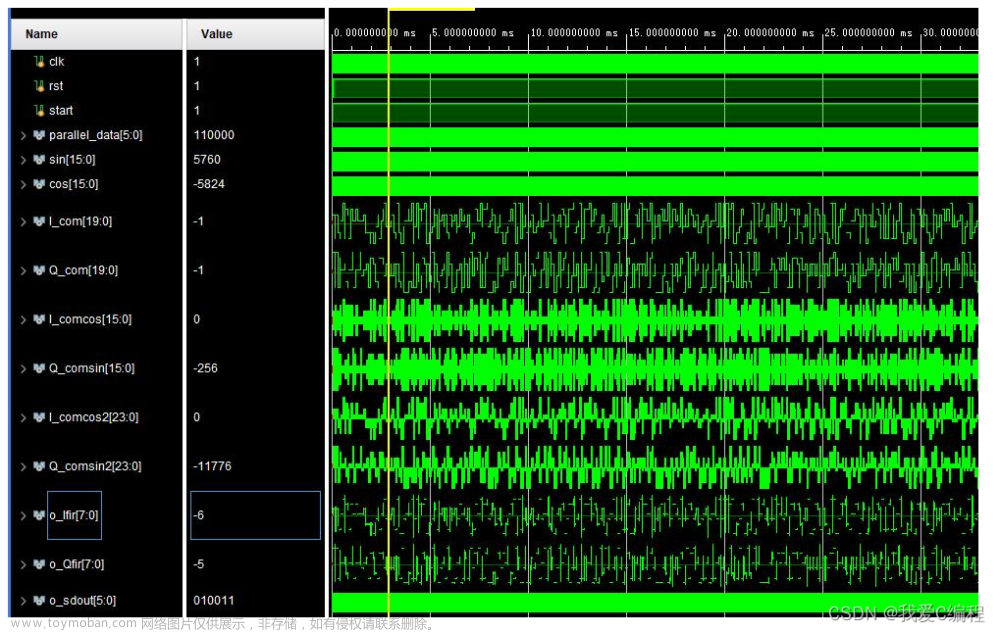

编写完测试激励之后,通过ModelSim仿真结果如下:

得到解调信号,然后通过Matlab和调制信号做比对,结果是一致,验证了解调的正确性文章来源:https://www.toymoban.com/news/detail-697789.html

文章来源地址https://www.toymoban.com/news/detail-697789.html

文章来源地址https://www.toymoban.com/news/detail-697789.html

到了这里,关于FSK解调技术的FPGA实现的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!