一、硬件布局指南

- 创造一个低噪音、功率稳定的环境

- 降低EMI/EMC的程度及其对RTL8211E/RTL8211EG的影响

- 简化信号跟踪的路由任务

1.1 布局

- RTL8211EG 必须尽可能靠近MAC(小于2.5英寸=6.35cm)

- 连接到RSET引脚的电阻器应靠近RTL8211E/RTL8211EG(小于800mils),并尽可能远离信号迹线(例如,VRRREG、REG_OUT、MDI0+/-、MDI1+/-等)和时钟信号(50mils min.)

- 如果MAC位于顶层,则PHY应位于底层,以避免散热器耦合

- RTL8211EG 到RJ45连接器的,MDI轨迹线必须小于12厘米

1.2 晶振

- 根据3W规则,晶振应放置在距离I/O端口、重要或高频信号迹线(TX、RX、电源)和磁性器件至少三倍于其自身宽度的位置

- 晶振的外屏蔽需要良好的接地,以避免电磁兼容/电磁干扰的感应,晶振的固定带(如有)也需要良好的接地。

- 每个PCB设计都有其独特的噪声耦合行为。铁氧体磁珠用于抑制功率噪声。建议用0Ω 电阻器代替磁珠 ,去耦电容器必须靠近电源引脚放置,以便IC电源引脚到电容器的距离小于200mils。

1.3 RX时钟

- RX时钟信号轨迹应尽可能短和宽。

- 在未断开的接地平面或电源平面附近布线时钟迹线。最大限度地减少过孔和层变化。

- RXC滤波器网络将EMI影响降至最低

1.4 MDI信号

- 从RTL8211E/RTL8211EG到10/100/1000M磁铁和RJ-45连接器的线路应尽可能短。

- 保持所有四个差分对信号迹线的匹配长度在800mil以内,MDI阻抗为50Ω共模,100Ω差模

- 每对的两个迹线应该彼此靠近放置(D1),因为它们是彼此的差分对信号并且对噪声提供强的消除效果。D1可以是两个差分迹线中的每一个的宽度。

- 不同差分对之间的间距应大于30mil,以最大限度地减少与其他对耦合的串扰(图中的D2)

- 接地平面屏蔽可用于分离所有四个信号对

- 为了最大限度地减少阻抗失配,我们建议不要在四个差分对上使用过孔

- 穿过平面分裂的信号(见图)可能会导致不可预测的返回路径电流,并可能导致信号质量故障,以及产生EMI问题 。

1.5 GMII(MII)/RGMII信号

- 尖锐的边缘可能会给电路增加意想不到的寄生效应。在快速能量爆发期间,减小迹线长度将减小迹线电感,不走90°直角信号线,

- 应仔细考虑地平面以上的迹线长度和迹线宽度与迹线高度之比。必须尽可能短(小于2.5英寸)

- 最好在这些迹线下面有一个接地平面。使用GND平面来包围它们是必要的。

- RXC和TXC是高速(125MHz)信号;在时钟和数据信号之间保持20mils的间隔。

- 将每个GMII(MII)/RGMII TX和RX(RXC/RXD/RXTL)组迹线长度匹配到100mils以内。

- 以50Ω阻抗布线GMII(MII)/RGMII迹线,并通过内层布线以减少辐射。

- 所有GMII(MII)/RGMII迹线必须参考一个完整的地平面。

- 将R1/C1靠近RTL8211E/RTL8211EG,将R2/C2靠近MAC(必须小于500mils)。

- RGMII迹线必须远离散热器。

- 将GMII(MII)/RGMII迹线路由到远离I/O迹线的位置,以避免串扰(>20mils)。

1.6 电源信号

RTL8211E/RTL8211EG数字电源引脚的电源可以通过去耦合电容器来改善。电源信号迹线(去耦合帽迹线、电源迹线、接地迹线)应尽可能短且宽。去耦合电容器的通孔的直径应该足够大。RTL8211E/RTL8211EG上的所有模拟电源引脚都需要与电容器断开耦合。解耦合电容器必须靠近RTL8211E/RTL8211EG(<200mils)放置,并且迹线应保持短。

- 连接到VDDREG的输入3.3V电源迹线必须大于40mils。

- 大容量去耦合电容器(Cin1和Cin2)必须放置在VDDREG的200mils(0.5cm)范围内,以防止输入电压过冲

- REG_OUT的输出功率轨迹必须大于60mils。

- Lx(2.2µH)必须保持在REGOUT的200毫米(0.5厘米)范围内。

- Cout1和Cout2必须保持在Lx的200mils(0.5cm)以内,以确保稳定的输出功率和更好的功率效率。

- 为了开关调节器的稳定性,电容器Cout1和Cout2必须是陶瓷(X5R)电容器。建议Cin1和Cin2为陶瓷电容器。

- 将Lx和Cin1放置在与RTL8211E/8211EG相同的图层上。不要在VDDREG和REGOUT迹线上使用过孔。

- 1.05V开关调节器输出引脚(REG_OUT)应仅连接到DVDD10和AVDD10(不要将此电源提供给其他设备)。

1.7 PCB层

PCB堆叠是影响产品EMC性能的主要因素,良好的堆叠可以非常有效地减少PCB上环路的辐射(差模发射)以及连接到板上的电缆的辐射(共模发射),另一方面,不良的叠加会大大增加这两种机制的辐射。

- 电源平面和接地平面应尽可能紧密地耦合。

- 信号层应始终与平面相邻,并且应紧密耦合(靠近)相邻平面。

- 高速信号(GMII/RGMII迹线)必须在平面之间的埋层上布线,以便平面可以充当屏蔽并包含来自高速迹线的任何辐射。

- 多个接地平面是非常有利的,因为它们将降低板的接地(参考平面)阻抗并减少共模辐射。

- 例如PCB为4层板。MDI和RGMII信号在层4和参考层3(GND平面)上布线。

例如PCB为6层板。 情况如下:

1.8 GND布局

不建议在模拟和数字接地域之间进行隔离,因为糟糕的接地平面分区可能会导致严重

的EMI发射,并由于弹跳噪声而降低模拟性能。

RTL8211E/RTL8211EG只有一个用于模拟电源(AVDD33和AVDD12)和数字电源(DVDD33和DVDD12)的接地平面。在IC的中心,有一个外露焊盘(EPAD)接地。PCB布局需要9个过孔将EPAD连接到下层接地平面。

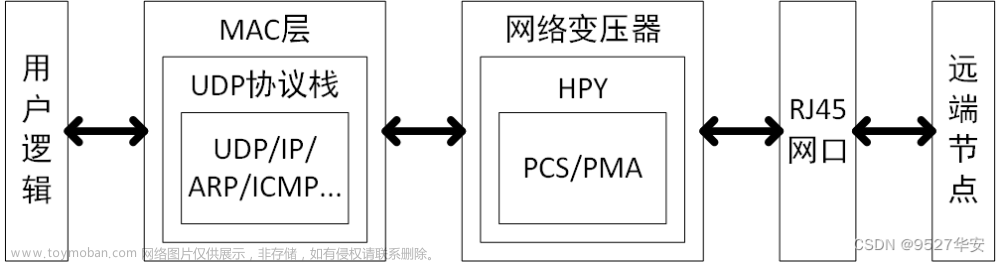

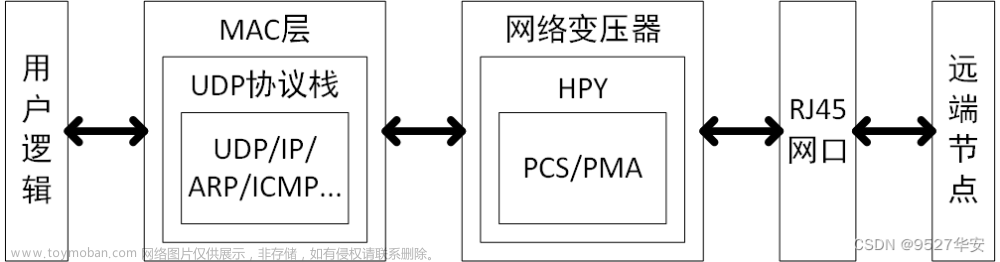

隔离器(网络变压器)下方的平面区域应保持空白 ,空隙区域是为了使变压器感应噪声远离电源和系统接地平面。重要的是保持底盘GND和系统GND之间的间隙(图中的D)大于60mils,以获得更好的隔离。文章来源:https://www.toymoban.com/news/detail-698781.html

文章来源地址https://www.toymoban.com/news/detail-698781.html

文章来源地址https://www.toymoban.com/news/detail-698781.html

到了这里,关于FPGA通信—千兆网(RTL8211EG)硬件layout的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!