【FPGA 约束:set_clock_groups 之异步时钟】——详细解析

FPGA 设计中,设置正确的时钟约束是非常重要的。在设计中,不同的时钟域之间都需要进行一定的同步和互锁,以保证系统能够正常工作。而异步时钟则是其中一个比较特殊的情况,其时序关系相对较为复杂,需要采用专门的约束方式来解决。本文将着重介绍 FPGA 约束中的 set_clock_groups 命令在异步时钟约束中的应用。

一、什么是异步时钟?

异步信号是指在时钟域之间没有明确的时序关系,两个信号之间既没有同步也没有互锁的机制。在异步时钟情况下,由于时序关系不确定,很容易产生一些奇怪的问题,例如互锁、冲突、抖动等。因此,在异步时钟情况下,必须采用专门的约束措施来限制其时序关系。

二、set_clock_groups 命令介绍

set_clock_groups 命令可用于设置时钟组规则,指定哪些时钟之间需要同步,哪些时钟之间不需要同步。该命令可以方便地将时钟域之间的时序关系进行约束。

通常,对于不同的时钟域,我们可以分别设置一个时钟组,并将这些时钟组之间的时序关系通过 set_clock_groups 命令进行描述。

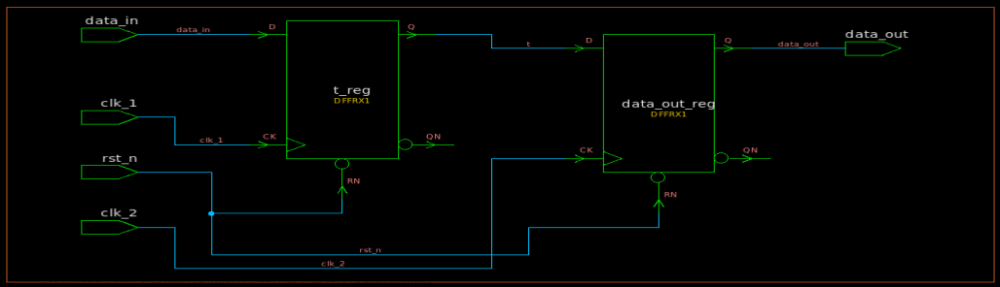

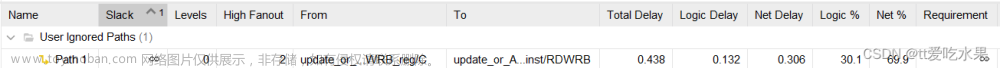

三、异步时钟的约束方法

在异步时钟情况下,由于时序关系不确定,需要采用特殊的约束方式。对于异步时钟,我们可以将其划分为两个时钟组:输入时钟组和输出时钟组。输入时钟组中包含异步时钟信号,而输出时钟组中则包含需要与异步时钟信号同步的时钟信号。文章来源:https://www.toymoban.com/news/detail-699791.html

set_clock_groups 命令的语法如下:文章来源地址https://www.toymoban.com/news/detail-699791.html

set_clock_groups -asynchronous [-group input_clk_grp] [-group output_clk_grp]

到了这里,关于【FPGA 约束:set_clock_groups 之异步时钟】——详细解析的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!