FPGA设计入门:Vivado综合简介

FPGA是一种基于可编程逻辑器件的数字电路设计技术,可以通过编程实现各种电路功能。Vivado是Xilinx公司推出的一款开发工具,可以用来对FPGA进行综合、布局、布线、生成比特流等操作。本篇文章将从Vivado综合的基本流程入手,详细介绍如何使用Vivado对FPGA进行综合。

一、综合的基本流程

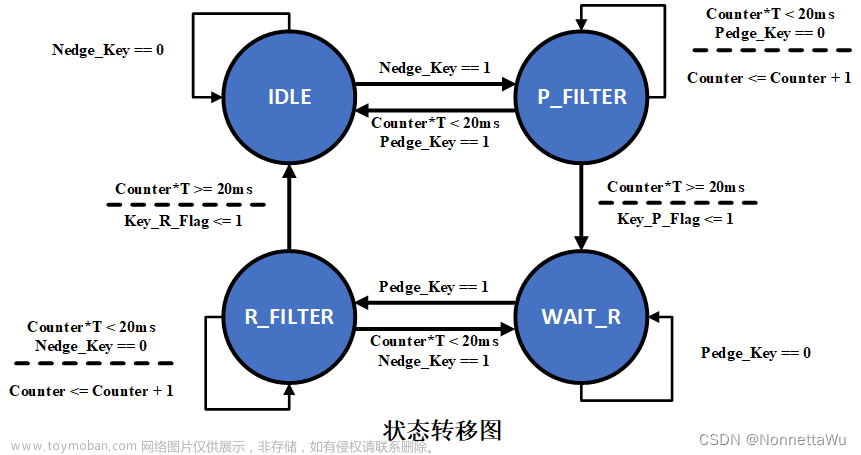

在Vivado中,综合是将RTL(硬件描述语言)代码转换成网表的过程,包括语法检查、逻辑优化、状态机提取、时序分析等步骤。下面是一个简单的VHDL代码示例:

entity adder is

port(a : in std_logic_vector(7 downto 0);

b : in std_logic_vector(7 downto 0);

c : out std_logic_vector(8 downto 0));

end entity;

architecture RTL of adder is

begin

c <= ('0' & a) + ('0' & b);

end architecture;

该代码表示了一个8位全加器,其中a、b为输入,c为输出。当收到综合指令后,Vivado会根据该代码自动生成网表,其中包含了模块的输入输出、模块间的连接关系、电路逻辑等信息。

二、综合的详细配置

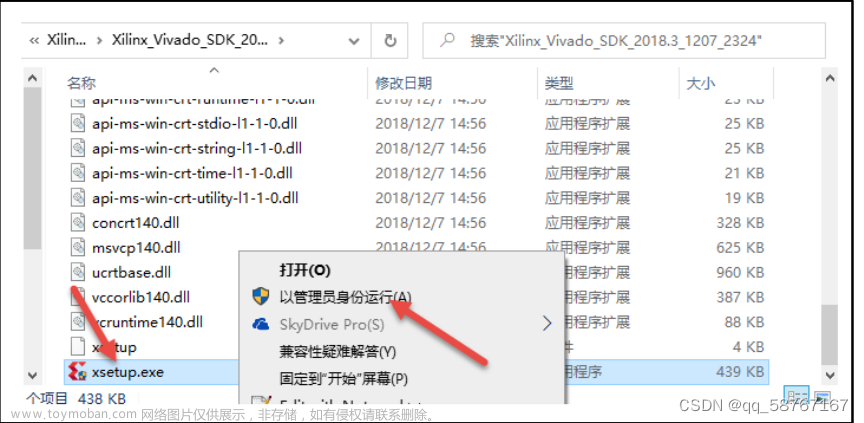

在Vivado中进行综合之前,需要先进行一些配置。第一步是打开Vivado工具,并创建一个新项目。接着,在创建的项目中加入设计文件,可以选择使用Vivado自带的编辑器创建文件,也可以将现有的RTL代码导入到项目中。文章来源:https://www.toymoban.com/news/detail-700060.html

在添加完设计文件后,需要进行一文章来源地址https://www.toymoban.com/news/detail-700060.html

到了这里,关于FPGA设计入门:Vivado综合简介的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!