spi接口在FPGA中应用的要点

SPI(Serial Peripheral Interface)接口是一种同步串行通信接口,广泛应用于数字系统中,包括FPGA中。下面是SPI接口在FPGA中应用的要点:

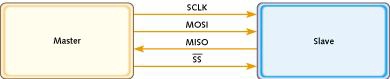

1、理解SPI协议:SPI接口是一种同步串行通信接口,包含一个主设备和多个从设备。主设备通过时钟信号控制数据传输,每次传输都由主设备发起。在传输时,主设备将数据发送给从设备,从设备将其接收并将响应数据发送回主设备。主设备和从设备通过四根线(CLK、MOSI、MISO、SS)进行通信。

2、熟悉SPI接口的硬件实现:FPGA中实现SPI接口的硬件通常包括时钟模块、状态机模块、数据收发模块等。时钟模块用于产生SPI时钟信号,状态机模块用于控制通信过程的状态转换,数据收发模块用于接收和发送数据。

3、熟悉SPI接口的软件实现:在FPGA中使用SPI接口进行通信,需要编写相关的Verilog代码或者其他硬件描述语言的代码来实现SPI接口的功能。在软件实现时需要考虑时序、数据传输的格式等问题。

4、确定从设备的地址和通信协议:在使用SPI接口通信时,需要确定从设备的地址和通信协议。在每次通信时,主设备需要向从设备发送一个地址来选择通信的从设备,然后按照从设备的通信协议进行数据传输。

5、确保时序正确:SPI接口是一种同步接口,因此在使用SPI接口进行通信时需要确保时序正确。特别是在高速通信时,时序问题容易导致数据传输错误。

总之,了解SPI接口的协议和硬件实现方式,熟悉SPI接口的软件实现,确定从设备的地址和通信协议,以及确保时序正确是使用SPI接口进行FPGA开发的重要要点。

SPI通信协议

SPI(Serial Peripheral Interface)通信协议是一种同步串行通信协议,通常由一个主设备和一个或多个从设备组成,它们通过四根线(CLK、MOSI、MISO、SS)进行通信。下面是SPI通信协议的详细说明:

1、时钟线(CLK):时钟线用于同步主设备和从设备的数据传输。时钟信号的频率由主设备控制,可以根据从设备的要求来进行调整。

2、主输出从输入线(MOSI):主设备通过MOSI线向从设备发送数据。每次传输时,主设备向MOSI线上发送一个位,从设备通过MISO线接收该位。MOSI线是单向的,只能由主设备输出。

3、从输出主输入线(MISO):从设备通过MISO线向主设备发送数据。每次传输时,从设备向MISO线上发送一个位,主设备通过MOSI线接收该位。MISO线是单向的,只能由从设备输出。

4、从设备选择线(SS):从设备选择线用于选定与主设备进行通信的从设备。当SS线被拉低时,主设备将选择与之连接的从设备进行通信。

SPI协议的传输过程如下:

1、主设备通过拉低某个从设备的SS线来选择通信的从设备。

2、主设备向MOSI线上发送一个起始位,从设备通过MISO线接收该位。

3、在后续的传输中,主设备和从设备通过时钟线同步传输数据。每次传输时,主设备向MOSI线上发送一个位,从设备通过MISO线接收该位。从设备也可以向MISO线上发送数据,供主设备接收。

4、当传输结束时,主设备通过拉高SS线来通知从设备结束本次通信。

SPI协议具有以下特点:

1、SPI通信协议是一种同步串行通信协议,传输速度较快。

2、主设备控制传输,每次传输都由主设备发起。

3、从设备通过SS线进行选择,可以支持多个从设备进行通信。

4、SPI通信协议通常采用全双工传输方式,主设备和从设备可以同时进行发送和接收数据。

总之,SPI通信协议是一种简单、快速、灵活的串行通信协议,被广泛应用于数字系统中。

下面是一个简单的Verilog代码,用于实现一个SPI主设备,向一个从设备发送数据:

module spi_master (

input wire clk, // 时钟信号

output wire cs, // 从设备选择信号

output wire mosi, // 主输出从输入信号

input wire miso, // 从输出主输入信号

input wire rst, // 复位信号

input wire [7:0] tx_data // 待发送的数据

);

reg [7:0] data_reg; // 数据寄存器

reg [3:0] state; // 状态机

parameter IDLE = 4'b0000; // 空闲状态

parameter START = 4'b0001; // 起始状态

parameter TRANSFER = 4'b0010; // 数据传输状态

parameter END = 4'b0011; // 结束状态

always @(posedge clk) begin

if (rst) begin

state <= IDLE;

data_reg <= 8'b0;

end

else begin

case (state)

IDLE: begin

cs <= 1'b1; // 禁用从设备

mosi <= 1'b0; // 发送起始位

state <= START;

end

START: begin

cs <= 1'b0; // 选定从设备

mosi <= 1'b0; // 发送起始位

state <= TRANSFER;

end

TRANSFER: begin

mosi <= data_reg[7]; // 发送数据位

data_reg <= {data_reg[6:0], 1'b0}; // 数据寄存器左移一位

state <= state + 1'b1; // 进入下一个状态

end

END: begin

cs <= 1'b1; // 禁用从设备

state <= IDLE; // 返回空闲状态

end

default: begin

state <= IDLE;

end

endcase

end

end

assign mosi = (state == START) ? 1'b1 : mosi; // 在起始状态发送“1”

endmodule

以上代码不建议直接copy使用

在空闲状态下,从设备选择信号(cs)和主输出从输入信号(mosi)都被拉高,等待传输开始。当SPI主设备收到一个发送数据的信号时,它将进入起始状态,向从设备发送一个起始位。然后,在数据传输状态下,它将按位发送待发送的数据,直到数据传输完毕。最后,它将进入结束状态,禁用从设备并返回空闲状态。

下面的Verilog代码,实现了一个SPI从设备,向SPI主设备发送数据:

module spi_slave (

input wire clk, // 时钟信号

input wire cs, // 从设备选择信号

input wire sclk, // 时钟信号

output wire miso, // 从输出主输入信号

input wire rst // 复位信号

);

reg [7:0] data_reg; // 数据寄存器

reg [3:0] state; // 状态机

parameter IDLE = 4'b0000; // 空闲状态

parameter START = 4'b0001; // 起始状态

parameter TRANSFER = 4'b0010; // 数据传输状态

parameter END = 4'b0011; // 结束状态

always @(posedge clk) begin

if (rst) begin

state <= IDLE;

data_reg <= 8'b0;

miso <= 1'b0;

end

else begin

case (state)

IDLE: begin

if (!cs) begin // 如果从设备被选中

state <= START; // 进入起始状态

end

end

START: begin

miso <= 1'b0; // 发送起始位

state <= TRANSFER;

end

TRANSFER: begin

if (sclk) begin // 如果时钟为高电平

data_reg <= {miso, data_reg[7:1]}; // 将数据存入寄存器中

miso <= data_reg[7]; // 发送寄存器中的最高位

if (data_reg == 8'hFF) begin // 如果所有数据都发送完毕

state <= END; // 进入结束状态

end

end

end

END: begin

if (!cs) begin // 如果从设备被选中

state <= START; // 回到起始状态

data_reg <= 8'b0; // 清空数据寄存器

miso <= 1'b0; // 清空输出

end

else begin

state <= IDLE; // 否则返回空闲状态

end

end

default: begin

state <= IDLE;

end

endcase

end

end

endmodule

以上代码不建议直接copy使用

在空闲状态下,从设备选择信号(cs)和从输出主输入信号(miso)都被拉低,等待SPI主设备的指令。当SPI主设备选定从设备时,从设备将进入起始状态,并向SPI主设备发送一个起始位。然后,在数据传输状态下,从设备将按位接收SPI主设备发送的数据,并将其存储在一个数据寄存器中。同时,从设备将在每个时钟周期中将最高位发送回SPI主设备。当所有数据都传输完毕时,从设备将进入结束状态。最后,在结束状态下,从设备将等待SPI主设备禁用它并返回到空闲状态。如果从设备在结束状态下再次被选中,则从设备将返回起始状态,重新发送数据。如果从设备在任何状态下被选中,但未收到有效指令,则从设备将返回空闲状态。文章来源:https://www.toymoban.com/news/detail-701672.html

可以具体的应用场景进行修改和扩展。例如,可以添加数据校验功能,以确保从设备发送和接收的数据的正确性;还可以添加中断功能,以便从设备能够及时响应SPI主设备的指令。文章来源地址https://www.toymoban.com/news/detail-701672.html

到了这里,关于浅析SPI在FPGA中的应用的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!