目录

逻辑框图(原理图)

端口约束和ILA

ILA waveform

实测波形

串口调试工具

源代码

顶层

逻辑框图(原理图)

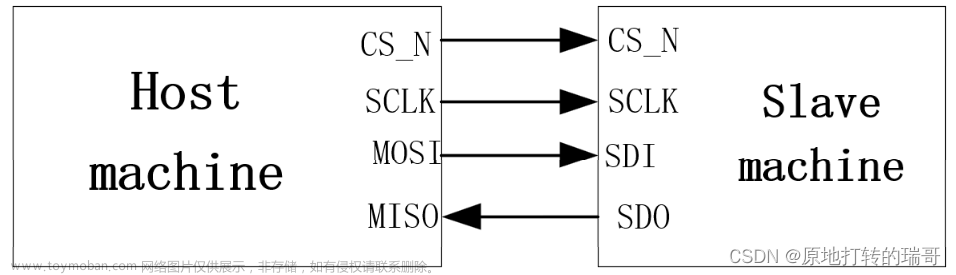

- FPGA和芯片之间通过三线SPI接口通信(DATA复用一个IO端口),FPGA和PC之间通过UART串口通信。

- 原理图包含4个模块,分别为:内建模块IBUFDS(用于将外部差分时钟转换为内部单端时钟)、UART接收模块uart_rx(用于从串口接收上位机发送的数据)、SPI收发模块spi_trx(用于将串口接收到的数据转换为SPI信号,根据芯片规定的SPI时序,FPGA发送(write)数据给芯片或从芯片回读(read)数据),UART发送模块uart_tx(用于将SPI回读到的数据从串口发给上位机)

-

原理图包含4个输入端口,分别为:差分时钟sys_clk_p和sys_clk_n,频率为200MHz(用于产生系统工作时钟);复位信号rst_n;UART输入端口uart_top_input(用于接收来自串口的数据)。

-

原理图包含5个输出端口,分别为:3个SPI端口spi_clk/spi_csn/spi_io(用于FPGA和芯片通信);UART输出端口uart_top_output(用于串口发送数据给上位机);led[3:0](用于串口调试)

端口约束和ILA

ILA waveform

- 根据不同的SPI时钟频率,需要设置不同的ILA波形采样深度,此处SPI时钟频率为1MHz,ILA采样深度设置为8192。

- 波形触发条件设置为信号spi_csn下降沿触发F(1 to 0 transition)。

实测波形

串口调试工具

自动识别串口COM7,波特率为9600,无校验位,8位数据位,1位停止位。文章来源:https://www.toymoban.com/news/detail-702302.html

源代码

顶层

`timescale 1ns / 1ps

module uart_spi_v10(

input sys_clk_p,

input sys_clk_n,

input rst_n,

input uart_top_input,

output [3:0] led,

output uart_top_output,

output spi_csn,

output spi_clk,

inout spi_io

);

wire [7:0] uart_rx_output;

wire [7:0] spi_data_rd;

IBUFDS #(

.DQS_BIAS("FALSE") // (FALSE, TRUE)

)

IBUFDS_inst (

.O(clk), // 1-bit output: Buffer output

.I(sys_clk_p), // 1-bit input: Diff_p buffer input (connect directly to top-level port)

.IB(sys_clk_n) // 1-bit input: Diff_n buffer input (connect directly to top-level port)

);

uart_rx_v10

#(

.BAUD_RATE (9600)

)

uart_rx_v10

(

.clk (clk),

.rst_n (rst_n),

.uart_rx_input (uart_top_input),

.uart_rx_output (uart_rx_output),

.uart_rx_valid (uart_rx_valid),

.uart_rx_stop (uart_rx_stop),

.led (led)

);

spi_trx_v10

#(

.FREQ_SPI_CLK (1_000_000)

//.FREQ_SPI_CLK (10_000_000)

)

spi_trx_v10

(

.clk (clk),

.rst_n (rst_n),

// from uart_rx

.spi_data_in (uart_rx_output),

.data_in_valid (uart_rx_valid),

// to device

.spi_csn (spi_csn),

.spi_clk (spi_clk),

.spi_io (spi_io),

// to uart_tx

.spi_data_rd (spi_data_rd),

.spi_rd_done (spi_rd_done)

);

uart_tx_v10

#(

.BAUD_RATE (9600)

)

uart_tx_v10

(

.clk (clk),

.rst_n (rst_n),

.uart_tx_input (spi_data_rd),

.spi_rd_done (spi_rd_done),

.uart_tx_output (uart_top_output)

);

endmodule

文章来源地址https://www.toymoban.com/news/detail-702302.html

到了这里,关于FPGA——实现三线SPI和UART的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!