Vivado仿真中输出高阻态FPGA故障分析与解决

在FPGA的设计中,Vivado仿真常常被用来验证设计的正确性。但是,有时候仿真结果会出现输出高阻态的情况,这个问题可能导致设计无法正常工作。本篇文章将详细分析这个问题出现的原因,并提供一些可能的解决方法。

问题描述

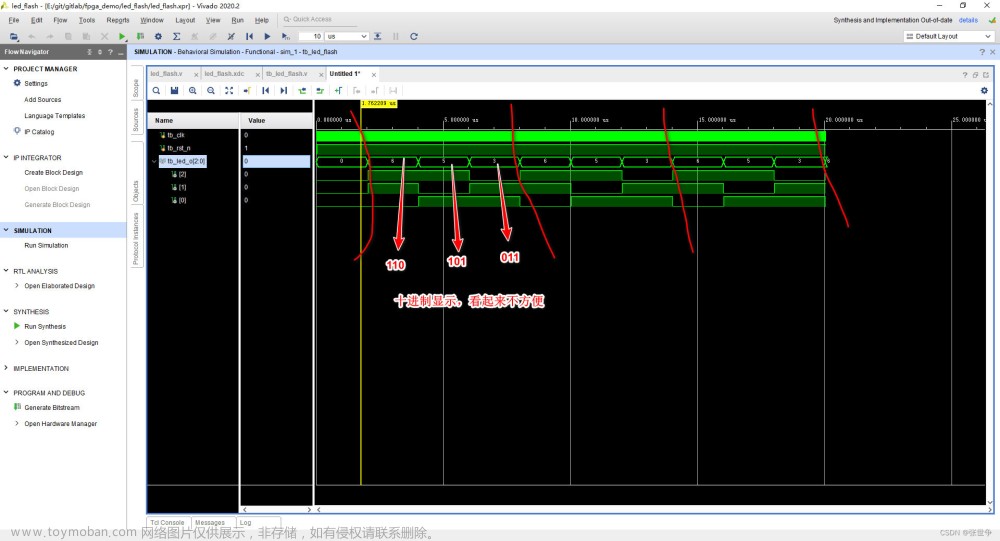

当我们进行Vivado仿真时,出现了网表输出高阻态的问题。具体的现象是输出信号处于高阻态,即输出信号没有电平状态,也就是无法判断是高电平还是低电平。这对于后续的设计和验证带来了很大的困难。

问题分析

原因1:仿真模型不完整或者错误

如果模拟模型中的某些部分没有被正确地建模或者缺失了重要的信号,就会导致仿真结果不准确。这种情况下,可以通过检查模型代码、信号定义以及仿真配置等方式来找到错误。

原因2:FPGA器件连接不正确

另一个可能的原因是FPGA器件连接不正确,例如信号引脚没有正确连接或者连接错误。在这种情况下,需要检查设计中的管脚定义和逻辑连接是否正确,以及信号引脚是否与其他模块正确连接。

原因3:仿真时间不够

有时候仿真时间不够可能会导致输出高阻态的问题。这种情况下,需要调整仿真时间或者增加仿真周期数,以保证仿真的充分性。文章来源:https://www.toymoban.com/news/detail-703112.html

原因4:仿真环境的限制

有时候仿真环境也可能会对仿真结果产生影响。例如,仿真中的时钟频率过高或者外部干扰噪声较大等原因。这种情况下,需要调整仿真环境的参数,以确保仿真环境与实际应用场景相符合。文章来源地址https://www.toymoban.com/news/detail-703112.html

解决方案

到了这里,关于Vivado仿真中输出高阻态FPGA故障分析与解决的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!