一、目录

1、matlab产生滤波器

2、matlab进行仿真

3、搭建vivado测试电路

4、vivado仿真

二、matlab产生滤波器

本文采用FIR低通滤波器,在命令行输入fdatool进入滤波器配置页面,如下配置

导出滤波器函数

设置名字为filter_3_4M

三、matlab进行仿真

1、产生两个信号2.5MHz和5MHz,然后对其进行混频,注意matlab中混频有两种方法,一种是两个信号相加,另一种是两个信号相乘,这两种混频结果是不同的

2、加法混频

dt=100000000;%采样点数

x=0:1/dt:0.00001;

f1=0.5*10^6;

f2=5*10^6;

s1=sin(2*pi*f1*x);

s2=sin(2*pi*f2*x);

s3=s1+s2;

figure(1);

subplot(3,1,1);

plot(s1);

title("0.5MHz")

subplot(3,1,2);

plot(s2);

title("5MHz")

subplot(3,1,3);

plot(s3);

title("加法混频信号")

Hd=filter_3_4M;

s4=filter(Hd,s3);

figure(2);

title("信号对比")

plot(x,s1,'g');%将0.5MHz与滤波后信号对比

hold on;

plot(x,s3,'y');

plot(x,s4,'r');

legend("0.5MHz","加法混频信号","滤波后信号")结果图

3、乘法混频

乘法混频输入信号为0.5MHz和5MHz,采用积化和差转换后的输出信号有两个输出频率,分别为4.5MHz和5.5MHz,由于之前设置的截止频率为4MHz,故理论上是不会产生滤波信号,接下来进行仿真验证

dt=100000000;%采样点数

x=0:1/dt:0.00001;

f1=0.5*10^6;

f2=5*10^6;

s1=sin(2*pi*f1*x);

s2=sin(2*pi*f2*x);

s3=s1.*s2;

figure(1);

subplot(3,1,1);

plot(s1);

title("0.5MHz")

subplot(3,1,2);

plot(s2);

title("5MHz")

subplot(3,1,3);

plot(s3);

title("乘法混频信号")

Hd=filter_3_4M;

s4=filter(Hd,s3);

figure(2);

title("信号对比")

plot(x,s1,'g');%将0.5MHz与滤波后信号对比

hold on;

plot(x,s3,'y');

plot(x,s4,'r');

legend("0.5MHz","乘法混频信号","滤波后信号")结果图

采用2.5MHz和5MHz信号进行乘法混频,可知混频后的频率为2.5MHz和7.5MHz,故经过滤波后应可获得2.5MHz的滤波结果

dt=100000000;%采样点数

x=0:1/dt:0.00001;

f1=2.5*10^6;

f2=5*10^6;

s1=sin(2*pi*f1*x);

s2=sin(2*pi*f2*x);

s3=s1.*s2;

figure(1);

subplot(3,1,1);

plot(s1);

title("2.5MHz")

subplot(3,1,2);

plot(s2);

title("5MHz")

subplot(3,1,3);

plot(s3);

title("乘法混频信号")

Hd=filter_3_4M;

s4=filter(Hd,s3);

figure(2);

title("信号对比")

plot(x,s1,'g');%将2.5MHz与滤波后信号对比

hold on;

plot(x,s3,'y');

plot(x,s4,'r');

legend("2.5MHz","乘法混频信号","滤波后信号")结果图

四、搭建vivado测试电路

1、产生vivado中filter IP核所需的滤波器参数coe文件

点击上面方框,按照下面进行配置

生成.coe文件

2、搭建电路

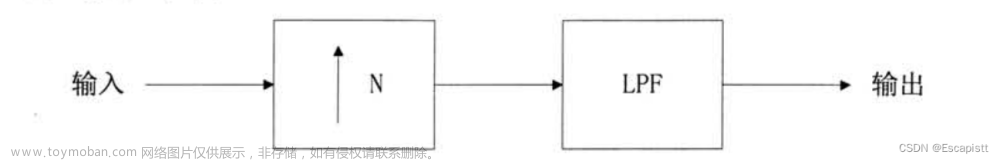

本电路采用2.5MHz和5MHz进行乘法混频,整体电路如下

3、IP核作用

DDS_compiler:产生测试所需正弦波

Multiolier:乘法器,用于将2.5MHz和5MHz进行混频

Utility Vector Logic:与门,两个信号输出同时有效时fir滤波器输入有效

RAM-based Shift Register:延时作用,乘法器计算需要1个时钟周期,为保持时序所用

Slice:截取信号,DDS产生的15位数据中低八位和高八位分别表示正余弦波,只用其中一个即可

FIR Compiler:滤波器IP

4、说明:由于IP核配置页面较多,此处不再一一截图,vivado工程文档链接为: 阿里云盘分享https://www.aliyundrive.com/s/Qm44pYvFNvx

五、vivado仿真

由于block design已经完成信号的输入和输出,故此仿真只需要添加时钟信号即可

module filter_tb();

reg clk;

wire [15:0] data_2_5m;

wire [15:0] data_5m;

wire [39:0] tdata;

wire [15:0] tdata_pre;

wire tdata_valid;

wire [7:0] wave_5m;

wire [7:0] wave_2_5m;

filter_wrapper filter_wrapper_inst(

.clk_100MHz(clk),

.data_2_5m(data_2_5m),

.data_5m(data_5m),

.tdata(tdata),

.tdata_pre(tdata_pre),

.tdata_valid(tdata_valid),

.wave_5m(wave_5m),

.wave_2_5m(wave_2_5m)

);

initial begin

clk=1'b0;

end

always #1 clk=~clk;

endmodule仿真结果:

附:

文章来源:https://www.toymoban.com/news/detail-703717.html

文章来源:https://www.toymoban.com/news/detail-703717.html

文章来源地址https://www.toymoban.com/news/detail-703717.html

到了这里,关于滤波器之matlab与vivado的联合仿真的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!