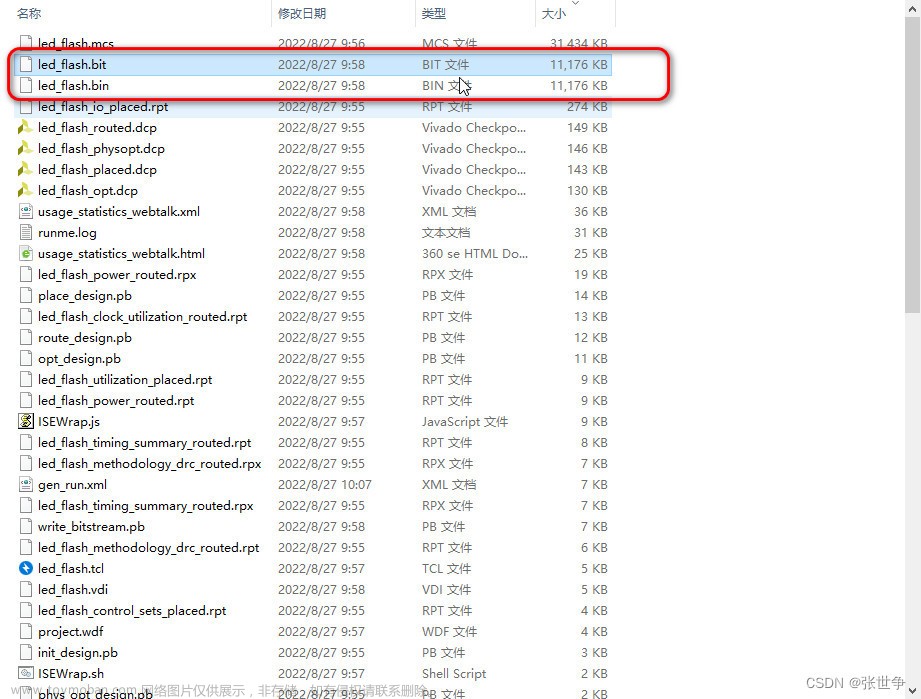

FPGA里面的可执行文件都涉及到 *.bit, *.mcs, *.bin 和 *.elf。

bit文件

bit 文件一般用于JTAG在线进行调试的时候,是把bit文件是烧写到FPGA中进行在线调试。

bin文件

bin 文件是二进制文件,按顺序只包含原始字节流,烧写进flash,上电加载自动加载。FPGA一般默认生成的是bit文件,bin文件生成是在ISE里property里勾选的,如下图所示。

而VIVADO中是可以在settings->Bitstream->-bin_file勾选即可。

mcs文件

mcs也是烧写到flash中的,上电后会自动加载到FPGA里,因此烧写进flash,需要断电重启。mcs文件是其中两个ASCII字符用于表示数据的每个字节HEX文件。mcs文件除了包含头部信息外还有地址信息以及校验码。

因此,MCS文件的效率似乎较低,因为它需要2个字节来表示1个字节。但是它有两个优点:

- 在每行的末尾都有一个校验和以确保完整性。

- 每行包括该行应位于内存中的地址。

如下图所示,VIVADO 中生成mcs文件,需要注意:

- Memory Part:所使用的Flash芯片型号

- Filename:生成的mcs文件名字,如果ila,还会生成prm文件

- Interface:选择flash加载模式

- Load Bitstream files:加载bit文件

- Start Address:下载flash的文件起始地址

- Write checksum,Disable bit swapping,Overwrite:小编一般都不勾选

- Command:Tcl指令,老鸟可以用tcl直接完成

elf文件

如果FPGA中用到 microblaze 或者 ZYNQ 的结构,还会有一个 elf 文件,这是因为其继承了 ARM 的可执行文件。

ARM 体系中,所有文件均采用的 ELF 文件格式。ARM 中的各种源文件(包括汇编文件,C 语言程序及 C++ 程序等)经过 ARM 编译器编译后生成 ELF 格式的对象文件(Object File)(.o文件)。这些对象文件(Object File)和相应的 C/C++ 运行时用到的库经过 ARM 连接器处理后,生成 ELF 格式的镜像文件(image),这种ELF 格式的映像文件是一种可执行文件,可被写入嵌入式设备的 ROM 中。

mcs文件和bin文件的区别

mcs文件里包含Bin文件的内容,但是mcs文件中,每行的开始有地址信息,最后一个byte是crc校验信息,所以mcs文件要比bin文件大。

但是烧录器烧写的时候,只烧录mcs文件中包含bin文件的那部分信息,不会将地址和crc烧录到flash中。

一般在烧写flash的时候,我们会用mcs文件,尤其是做multiboot和fallback的时候,因为mcs文件中包含有地址信息,会告诉烧录器,golden image放在哪里,multiboot image放在哪里文章来源:https://www.toymoban.com/news/detail-704574.html

bit文件和bin文件的区别

bin文件不包含头部信息,bit为bin+头部信息(工程名称以及时间等信息)。文章来源地址https://www.toymoban.com/news/detail-704574.html

到了这里,关于bit、bin 、mcs文件区别的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!