整体架构:micro blaze 、AXI UART 、AXI SPI;

语言:Verilog 、C

开发软件:vivdao2019.1

接口:UART 、SPI 、QUAD SPI文章来源地址https://www.toymoban.com/news/detail-705141.html

- uart

通用异步收发器(Universal Asynchronous Receiver/Transmitter:UART)

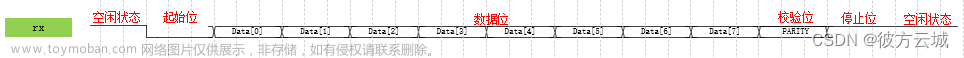

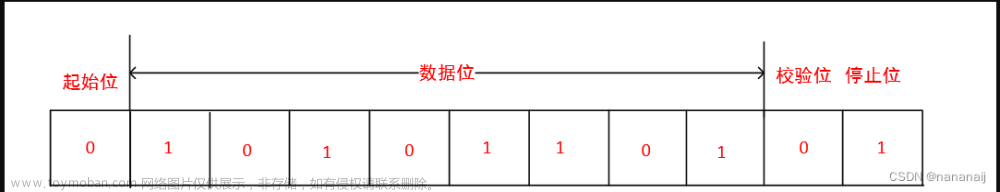

UART首先将接收到的并行数据转换成串行数据来传输。消息帧从一个低位起始位开始,后面是5~8个数据位,一个可用的奇偶位和一个或几个高位停止位。接收器发现开始位时它就知道数据准备发送,并尝试与发送器时钟频率同步。如果选择了奇偶,UART就在数据位后面加上奇偶位。奇偶位可用来帮助错误校验。 在接收过程中,UART从消息帧中去掉起始位和结束位,对进来的字节进行奇偶校验,并将数据字节从串行转换成并行。UART也产生额外的信号来指示发送和接收的状态。例如,如果产生一个奇偶错误,UART就置位奇偶标志。

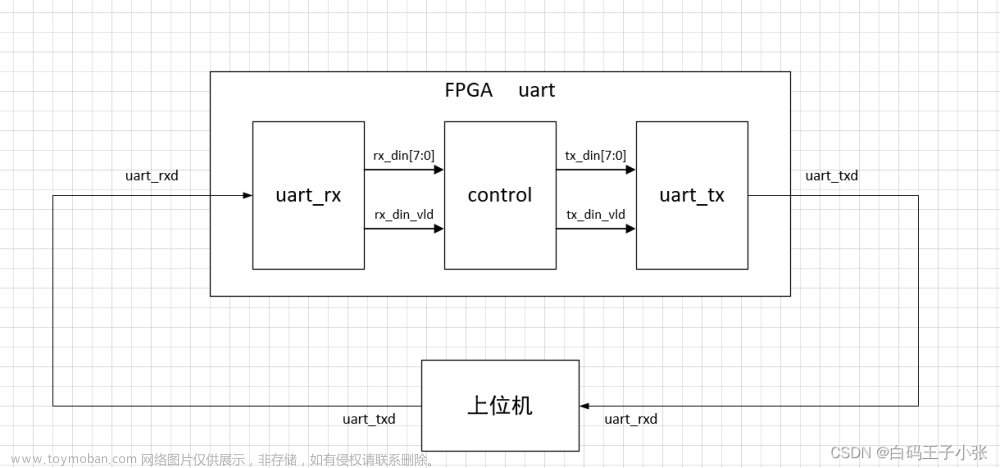

在本文中,FPGA实现了UART的包接收和数据缓存,接收模块采用了microblaze+axi uart实现,在SDK端采用C语言实现接收;包数据的缓存采用循环队列fifo实现。具体缓存数据的字节大小依据项目大小分配;

接收数据的触发条件:中断触发,即uart接收第一个数据后查看uart的状态寄存器,判断状态寄存器的数据有效性,即中断触发,进入到中断后,通过UART的接收函数接收数据,接收一定字节的数据后进行数据的打包处理,打包的数据存储在循环队列中,等待flash从循环队列中取数据,完成第一包数据的写入。 - flash

快闪存储器(英语:flash memory),是一种电子式可清除程序化只读存储器的形式,允许在操作中被多次擦或写的存储器。这种科技主要用于一般性数据存储,以及在计算机与其他数字产品间交换传输数据,如储存卡与U盘。闪存是一种特殊的、以宏块抹写的EPROM。早期的闪存进行一次抹除,就会清除掉整颗芯片上的数据。

flash的应用场景(基于FPGA):主要用于FPGA程序的固化模块,即将程序固化到flash中,断电重启后FPGA会从flash中加载程序,完成FPGA的启动;

flash的原理:FPGA需要固化的MCS、BIN、BIT文件的数据按照最小存储单元存到flash中,完成FPGA固化文件的存储;具体操作流程如下:FPGA需要固化程序时在vivado软件扫到配置flash的具体器件,然后再软件设置界面选择配置flash的型号和配置方式,配置的流程为flash器件的擦除、写数据、写入数据的校验。

flash的结构:flash的最小存储单元为sub sector(子扇区),每个sub sector包含4K的存储空间(4096个字节),block称为块(包含16个sub sector,存储空间大小为64K),对于16M的flash共有256个block(16777216个字节的存储空间)。

flash的擦除、写、读:

(1)擦除:擦除分为Subsector erase(SSE)、sector erase(SE)、Bulk erase(BE)三个部分的擦除,

✔Subsector erase:子扇区擦除,擦除命令为20h。按起始地址往后擦除4K大小的空间,擦除完成后4K大小的每个page的数 据为0xFF。

✔sector erase:扇区擦除,擦除命令为D8h。按起始地址往后擦除64K大小的空间,擦除完成后64K大小的每个page的数据为0xFF。

✔Bulk erase:全擦除,擦除命令为C7h。擦除完成后全flash为0xFF。

(2)写:扇区擦除完成后,开始数据的写入,数据的写入按照写入的最小单元page(页)进行写入,写入命令为02h。

(3) 读:从起始地址读数据,每次读出一个扇区的数据(64K),读数据的命令为03h。

(4)注意**:flash的全擦除后不能立即写数据,需要等flash为空闲状态的时候再写入数据**。

flash的分区:flash的分区是为了将要更新的程序和引导程序进行区域划分,是进行uart更新flash程序的关键部分,具体的流程为:

(1)将引导程序从flash的0x000000(flash的大小为16M,地址线宽度为24位)存储下来,给足够的引导程序存储空间(如程序大小为2K,则需要预留大于2K的程序存储空间),这样每次上电后FPGA程序从flash的0地址开始加载,可以执行后续的远程更新操作;

(2)开始需更新程序的远程更新,按照flash的擦除和写操作将数据写入到flash的后续地址中,例如从0x400000开始写数据;

(3)在FPGA端使用ICAP源语按照具体的命令使FPGA从已经写入程序的起始地址开始加载新的程序。

(4)

文章来源:https://www.toymoban.com/news/detail-705141.html

到了这里,关于基于FPGA的flash远程UART更新的实现的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!