一、了解全加器

1、简介

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。

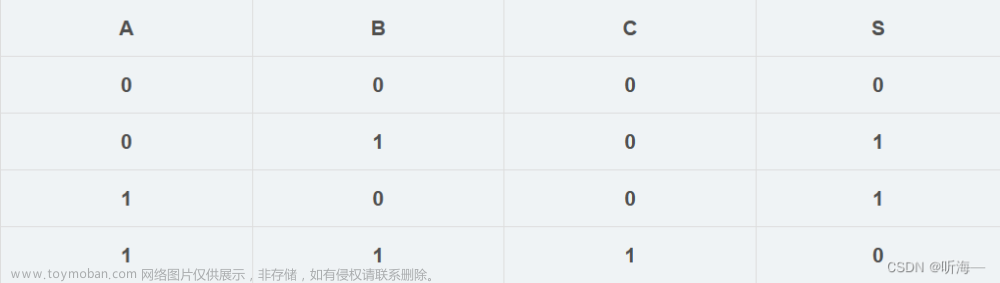

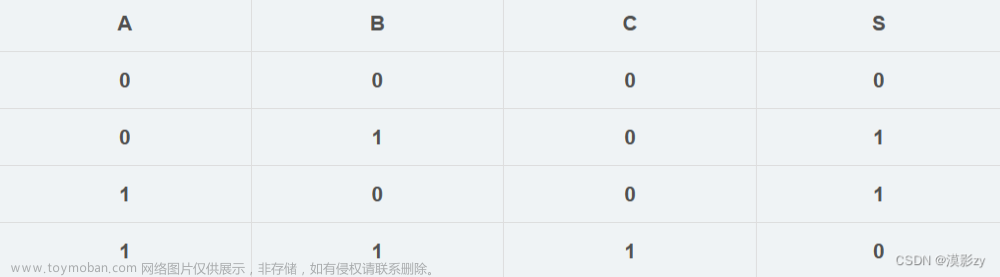

2、真值表

一位全加器为例

Ain表示被加数,Bin表示加数,Cin表示低位进位,Cout表示高位进位,Sum表示本位和

| Ain | Bin | Cin | Cout | Sum |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

3、表达式

Sum=Ain⊕Bin⊕Cin

C o u t = ( A i n ⊕ B i n ) ⋅ C i n + A i n B i n = ( A i n & B i n ) ∣ ( B i n & C i n ) ∣ ( A i n & C i n )

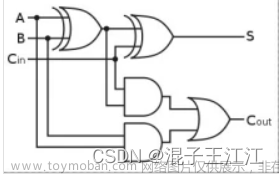

4、原理图

二、原理图实现全加器

1、创建工程文件

注意芯片的选择

2、原理图输入

(1)设置半加器

进入绘制

元件选择

选择元件有

and2、xor、input、output

保存并编译文件

查看电路图

设置为调用元件

(2)全加器绘制

元件选择:

half_adder,or2,input,output

实现效果

3、仿真实现

(1)添加波形文件

(2)添加信号

(3)编辑信号

(4)保存并仿真

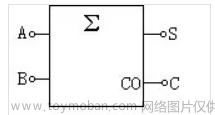

三、Verilog实现加法器

1、创建verilog文件

2、代码实现

module full_adder(

//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位

input ain,bin,cin,

//输出信号,cout表示向高位的进位,sum表示本位的相加和

output reg cout,sum

);

reg s1,s2,s3;

always @(ain or bin or cin) begin

sum=(ain^bin)^cin;//本位和输出表达式

s1=ain&cin;

s2=bin&cin;

s3=ain&bin;

cout=(s1|s2)|s3;//高位进位输出表达式

end

endmodule

3、数字电路图

4、仿真实现

按照上文同样方法实现波形仿真

5、下载测试

四、实现四位全加器

1、创建文件

2、编写代码

module adder_4(cout,sum,a,b,cin);

output[3:0] sum;

output cout;

input[3:0] a,b;

input cin;

assign {cout,sum}=a+b+cin;

endmodule

3、编译实现

4、下载测试

文章来源:https://www.toymoban.com/news/detail-707275.html

文章来源:https://www.toymoban.com/news/detail-707275.html

五、参考与总结

参考

https://blog.csdn.net/qq_43279579/article/details/115480406

总结

本次实验通过原理图和verilog两种方式实现全加器,并且进一步实现了4位全加器

了解了FPGA的基本操作文章来源地址https://www.toymoban.com/news/detail-707275.html

到了这里,关于FPGA基础——全加器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!