一、 概述

二、 端口说明[此章节为引用]

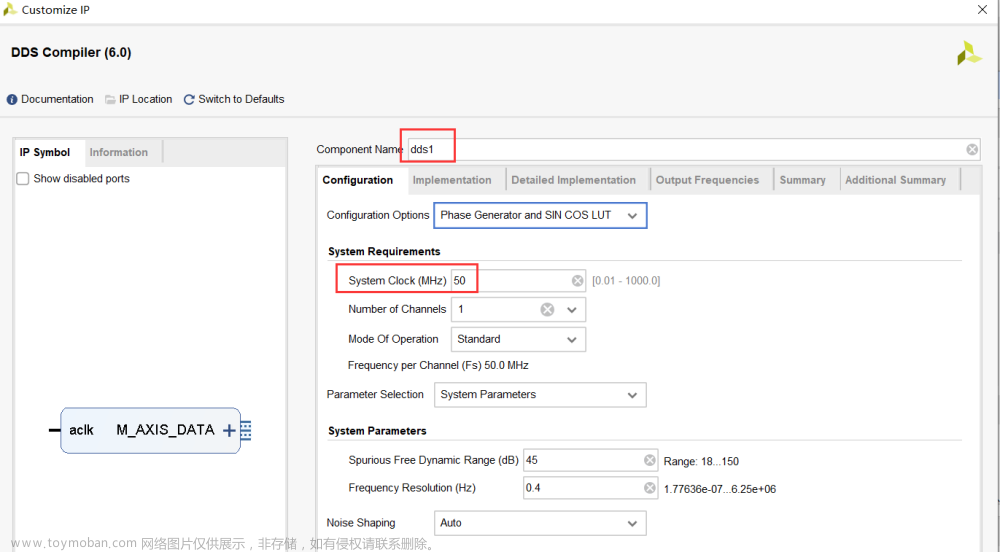

三、 ip核的生成

四、 matlab中cic滤波器的设计

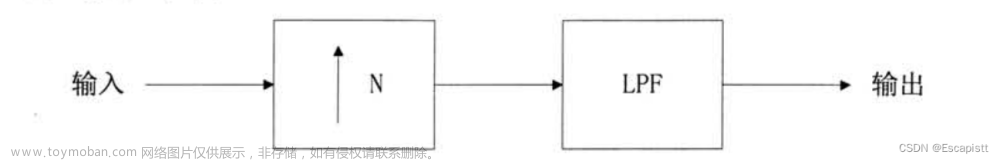

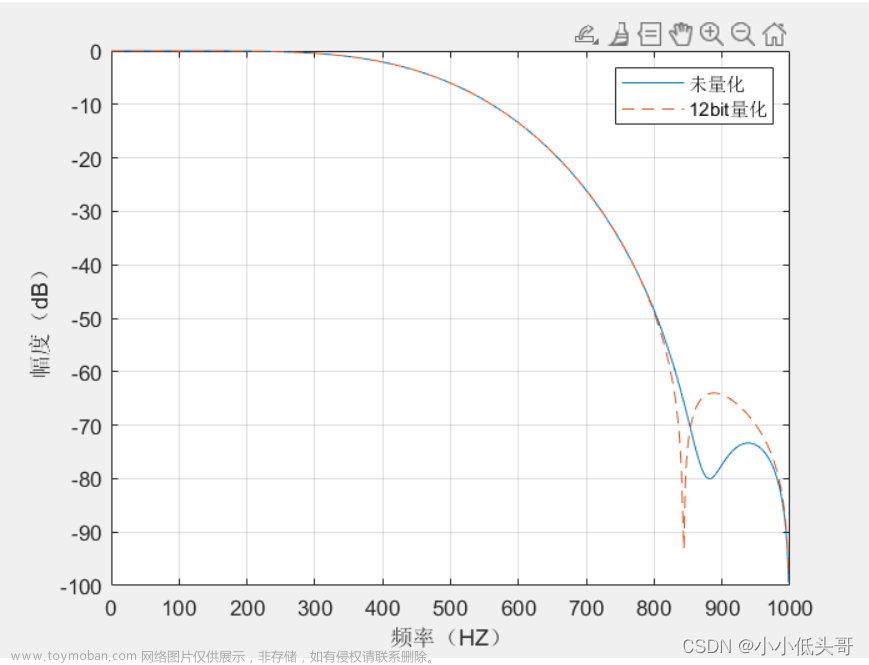

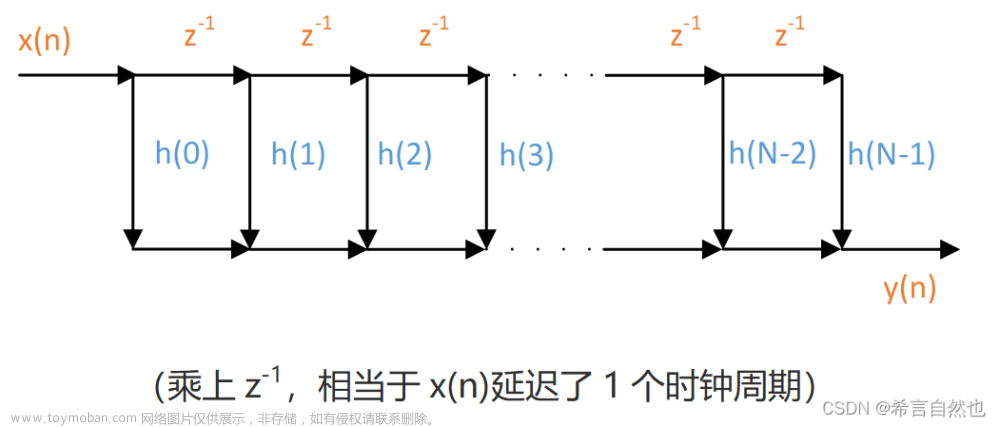

此部分来源于博客

总接:

四、仿真

第一组 :

采样率0.2MHZ,信号频率1Khz,抽取倍数5倍。

主程序:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/07/18 21:09:15

// Design Name:

// Module Name: cic_ip_test

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module cic_ip_test();

reg aclk;

reg [15:0] s_axis_data_tdata;

reg s_axis_data_tvalid;

wire s_axis_data_tready;

wire [23:0] m_axis_data_tdata;

wire m_axis_data_tvalid;

parameter data_num=4000; //仿真数据长度

reg signed [9:0] stimulus[data_num-1:0];

integer i;

/*********************时钟的产生***********************/

parameter period=10;

initial aclk =0;

always #(period/2) aclk=~aclk;

/*********************信号的初始化***********************/

initial begin

s_axis_data_tvalid<=1'b0;

s_axis_data_tdata <= 16'd0;

$readmemb("E:/vivado_project/cic/cic_test/E6_4_sin_in.txt",stimulus);

# period;

# period;

i=0;

end

/*********************将数据送入cic ip核***********************/

always@(negedge aclk) begin //注意下降沿

if(i==data_num-1 && s_axis_data_tready==1'b1) begin

s_axis_data_tdata <= {{6{stimulus[i][9]}},stimulus[i]};

s_axis_data_tvalid <= 1'b1;

i<=0;

end

else if(s_axis_data_tready==1'b1 && i<data_num-1) begin

s_axis_data_tdata <= {{6{stimulus[i][9]}},stimulus[i]};

s_axis_data_tvalid <= 1'b1;

i <= i+1;

end

else begin

s_axis_data_tvalid <= 1'b0;

s_axis_data_tdata <=s_axis_data_tdata;

i <= i;

end

end

/*********************cic ip的例化***********************/

cic_compiler_0 cic_compiler_inst0 (

.aclk(aclk), // input wire aclk

.s_axis_data_tdata(s_axis_data_tdata), // input wire [15 : 0] s_axis_data_tdata

.s_axis_data_tvalid(s_axis_data_tvalid), // input wire s_axis_data_tvalid

.s_axis_data_tready(s_axis_data_tready), // output wire s_axis_data_tready

.m_axis_data_tdata(m_axis_data_tdata), // output wire [23 : 0] m_axis_data_tdata

.m_axis_data_tvalid(m_axis_data_tvalid) // output wire m_axis_data_tvalid

);

/*********************将最终的结果输出***********************/

integer w_file;

always@(posedge m_axis_data_tvalid) begin

w_file = $fopen("E:/vivado_project/cic/cic_test/E6_4_sin_out.txt");

$fdisplay(w_file,"%d",$signed(m_axis_data_tdata[16:0])); //h代表16进制 d代表十进制

end

endmodule

仿真结果

从图中可以看出,输出与输入相比经过了5倍的抽取。文章来源:https://www.toymoban.com/news/detail-707671.html

同理第二组 :

采样率0.2MHZ,信号频率1Khz,内插倍数5倍。

从图中可以看出,输出与输入相比经过了5倍的内插。

另外输出数据位宽和输入数据位宽估算公式为:

其中B为输入信号的位数,Bmax为输出信号的最大位宽。

第三组:

采样率0.2MHZ,信号频率1Khz和50khz,抽取倍数5倍。

可以看出50KHZ处,比最大值低了大约41dB。

从结果可以看出,50khz的频率成分被滤掉,并且输出采样率降低为原来的五分之一。文章来源地址https://www.toymoban.com/news/detail-707671.html

五、 参考资料

- CIC滤波器

- Matlab中CIC滤波器的应用

- CIC滤波器(公式推导)

- 基于FPGA的CIC滤波器设计(1)(重点看)

- Vivado CIC IP核滤波器详解(一)(重点中的重点)

- 多通道CIC抽取滤波器Vivado CIC IP核实现实现(3)

- FPGA数字信号处理(十九)Vivado CIC IP核实现

- FPGA数字信号处理(十六)单级CIC滤波器Verilog设计(仿真重点)

-

FPGA数字信号处理(十七)多级CIC滤波器Verilog设计

10.插值滤波器设计(抽取和插值的理论,很重要)

到了这里,关于【FPGA】:ip核-----CIC滤波器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!