一.以太网概述

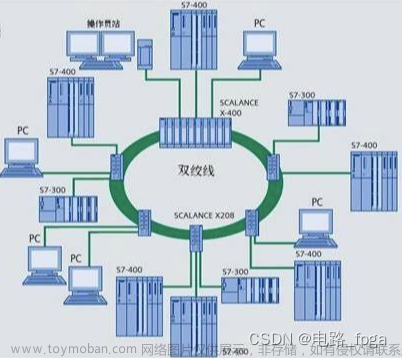

以太网(Ethernet)是当今局域网采用的最通用的局域网标准。它规定了包括物理层的连线,电子信号和介质访问协议的内容。它具有成本低,通信速率快,抗干扰性强的特点。

以太网主要分为:

- 标准以太网:10Mbit/s

- 快速以太网:100Mbit/s

- 千兆以太网:1000Mbit/s

以太网的接口主要有RJ45,RJ11,SC光纤接口等等。其中RJ45是我们最常见的网络设备接口。

RJ45是布线系统中信息插座(即通信引出端)连接器的一种,连接器由插头(接头、水晶头)和插座(模块)组成,插头有8个凹槽和8个触点。RJ是Registered Jack的缩写,意思是“注册的插座”。在FCC(美国联邦通信委员会标准和规章)中RJ是描述公用电信网络的接口,计算机网络的RJ45是标准8位模块化接口的俗称。

二.接口与时序

2.1 MII接口与时序

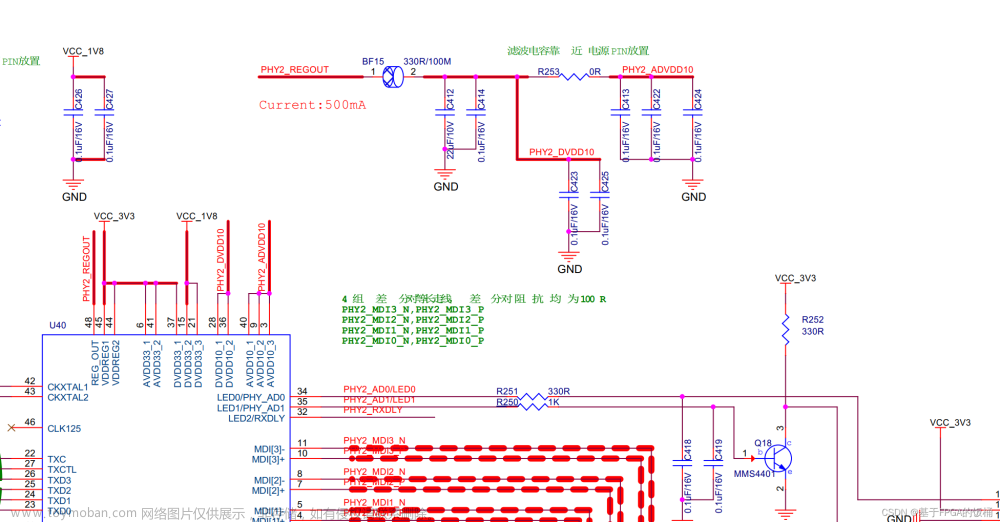

2.1.1 PHY 芯片

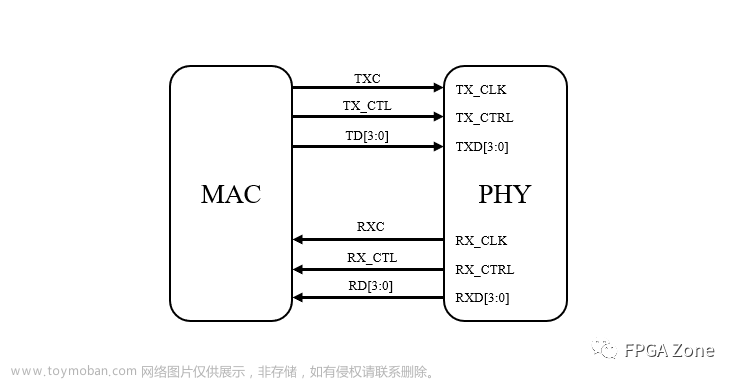

PHY芯片在发送数据时,首先将MAC发过来的并行数据转化为串行流数据,按照物理层的编码规则把数据编码转换成模拟信号通过网口发送出去,接收数据的流程反之。

当我们给网卡接入网线的时候,PHY芯片不断发出脉冲信号来检测对端是否有设备,它们通过标准的“语言”交流,互相协商并确定连接速度、双工模式、是否采用流控等。通常情况下,协商的结果是两个设备中能同时支持的最大速度和最好的双工模式。这个技术被称为Auto Negotiation, 即自动协商。

2.1.2 MII接口

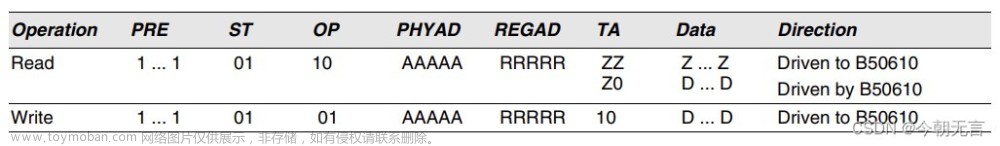

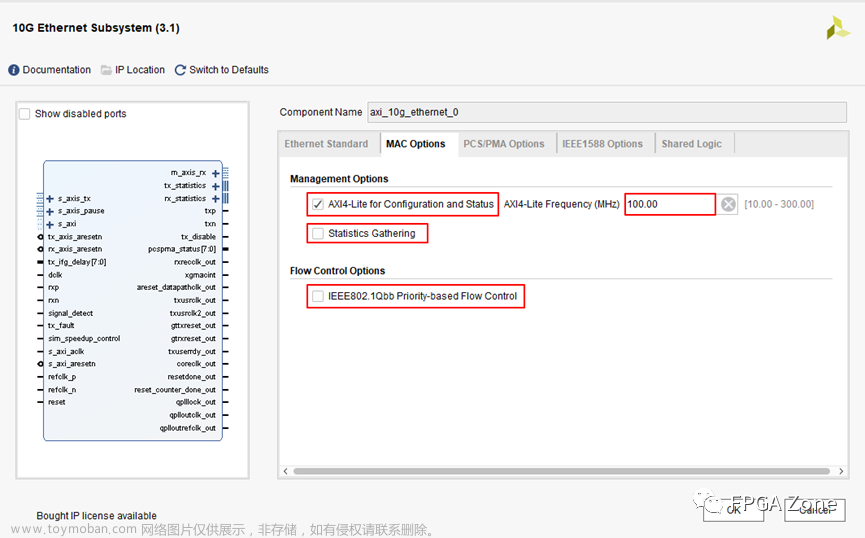

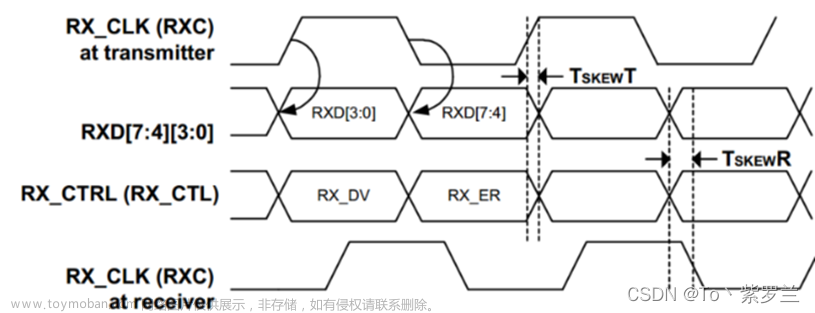

MII即媒体独立接口,也叫介质无关接口。它是IEEE-802.3定义的以太网行业标准。它包括一个数据接口,以及一个MAC和PHY之间的管理接口。数据接口包括分别用于发送器和接收器的两条独立信道。每条信道都有自己的数据、时钟和控制信号。MII数据接口总共需16个信号。管理接口是个双信号接口:一个是时钟信号,另一个是数据信号。通过管理接口,上层能监视和控制PHY。

RMII接口是MII接口的一种简化版本。

三.以太网通信协议

3.1 以太网数据格式

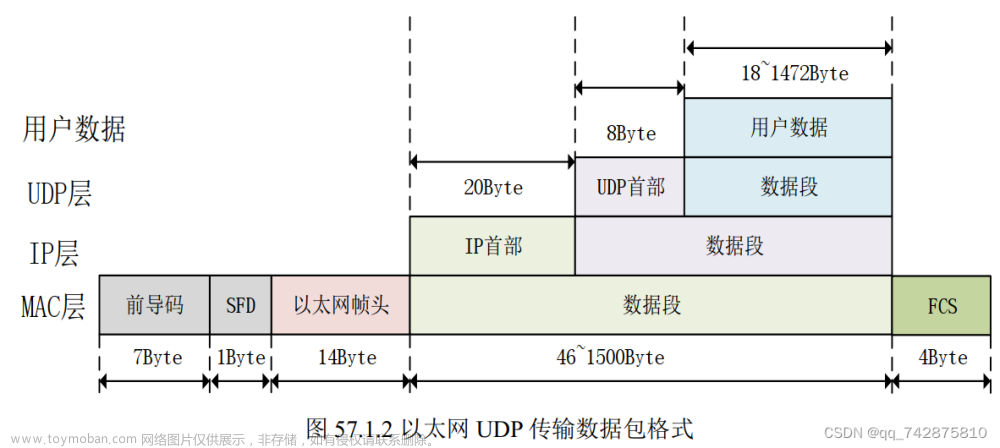

- 物理层:为数据端设备提供原始的比特流通路。

- 数据链路层:数据格式,错误检测和纠正。

- 网络层:IP寻址找到端口和端口的连接。

- 传输层:建立连接。UDP和TCP就是传输层。

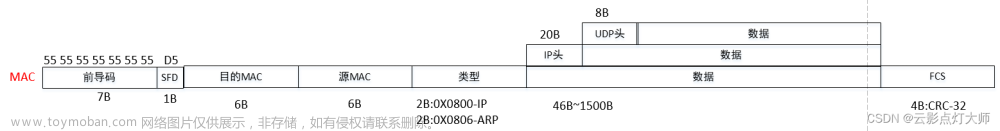

- 以太网帧头包括6个字节的源MAC地址,6个字节的目的MAC地址,两个字节的长度/类型。

帧间隙(IFG, Frame Check Sequence)为接收下一帧做准备的时间,IFG的最小值是96 bit time。

10Mbit/s 最小时间是9600ns

100Mbit/s 最小时间是960ns

1000Mbit/s,最小时间是96ns

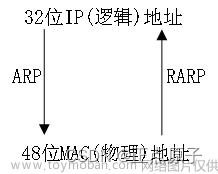

3.2 IP协议

IP协议:Internet Protocol (互联网协议/网际协议) IP协议是TCP/IP协议簇中的核心协议,IP协议规定了数据传输时的基本单元和格式。IP协议位于以太网MAC帧格式的数据段,IP协议内容由IP首部和数据字段组成。所有的TCP,UDP,ICMP数据都是以IP数据报格式传输。

文章来源:https://www.toymoban.com/news/detail-709564.html

文章来源:https://www.toymoban.com/news/detail-709564.html

3.3 UDP协议

3.3.1 UDP/TCP区别

文章来源地址https://www.toymoban.com/news/detail-709564.html

文章来源地址https://www.toymoban.com/news/detail-709564.html

到了这里,关于FPGA之以太网详解的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!