FPGA-结合协议时序实现UART收发器(一):UART协议、架构规划、框图

记录FPGA的UART学习笔记,以及一些细节处理,主要参考奇哥fpga学习资料。

本次UART主要采用计数器方法实现,实现uart的稳定性发送和接收功能,最后实现串口数据回环进行功能测试。

一、UART协议

UART协议如图。

包含:空闲位、起始位、数据位、校验位、停止位、空闲位(一般没有)

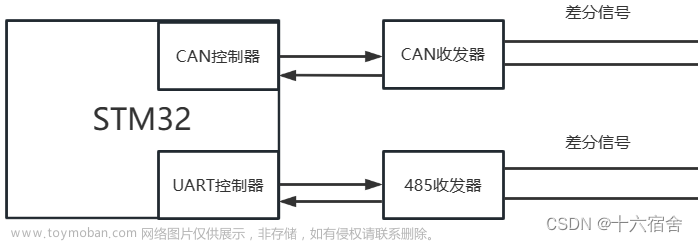

二、架构框图

对于规划架构框图时,从整体再到细节考虑,即从大到小;

对于具体代码实现时,从小模块代码再到顶层,即从小到大。

UART整体架构框图如下。 文章来源:https://www.toymoban.com/news/detail-709728.html

文章来源:https://www.toymoban.com/news/detail-709728.html

总结

通过对照UART协议和时序,以及规划好的架构框图来一步步从小到大实现整体功能。文章来源地址https://www.toymoban.com/news/detail-709728.html

到了这里,关于FPGA-结合协议时序实现UART收发器(一):UART协议、架构规划、框图的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!