根据FPGA使用的要点,GT/Serdes/高速收发器这样的关键词,进行检索,及FPGA的接口培训信息,整理成表如下:文章来源地址https://www.toymoban.com/news/detail-714122.html

| 序号 | 一级搜集 | 二级搜集 | 引申 |

|---|---|---|---|

| 1 | 知乎ID FPGA个人练习生 | FPGA实现图像去雾 基于暗通道先验算法 纯verilog代码加速 提供2套工程源码和技术支持 没玩过GT资源都不好意思说自己玩儿过FPGA,这是CSDN某大佬说过的一句话,鄙人深信不疑。。。GT资源是Xilinx系列FPGA的重要卖点,也是做高速接口的基础,不管是PCIE、SATA、MAC等,都需要用到GT资源来做数据高速串化和解串处理,Xilinx不同的FPGA系列拥有不同的GT资源类型,低端的A7由GTP,K7有GTX,V7有GTH,更高端的U+系列还有GTY等,他们的速度越来越高,应用场景也越来越高端 | 免责声明写的挺有意思 本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。 他是各种投稿 在职场问题下也写技术专栏 知乎提问 FPGA工程师为什么这么难招? 我的评论是FPGA应用场景少,对个人发展不利,只有成为高手,自己搞定全套,要么就是asic能量产 |

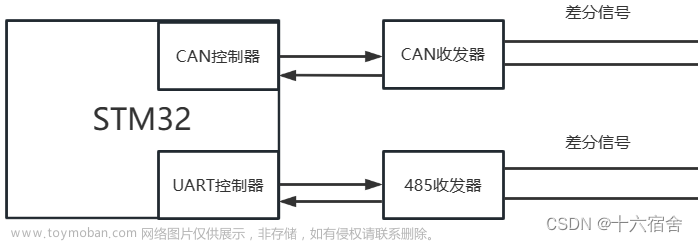

| 2 | 我培训的感受 serdes输出的时钟,为什么要输出,因为它同时解出来数据和时钟,只有输出时钟是和数据同步的 | Serdes用于点对点高速传输 我FPGA里出光的时候 FC各节点之间是serdes,还有pcie srio这些协议底层都是serdes,最简单的是xilinx提供的Aurora协议 Serdes是时钟是专用晶振出来的,要效果特别好的晶振 | Serdes里面都有数据包 数据包就有头部、数据和尾部 Xilinx7系列 serdes用的时候分组 quad概念,能用QPLL就不要用CPLL(这点我看手册看代码的时候没有意识到,不知怎的印象是CPLL好) 看图要看懂 注意FPGA逻辑端用的是RXUSRCLK2,看图片就能看出来,我之前没注意 极性 如果发现电路板极性反了,可以有个容错手段,把极性勾选,通过逻辑反向一下解决此问题 眼图 它是示波器显示的信号波形长时间叠加起来构成的,余辉功能:一直记录之前信号 我们做模块 最后对外接口是axi,统一标准。这也是实操过程中组里大佬提过的 |

文章来源:https://www.toymoban.com/news/detail-714122.html

到了这里,关于“GT/Serdes/高速收发器”相关的FPGA调研的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!