目录

前言

一、四选一多路选择器原理

二、原代码

1.Verilog源码

2.测试文本

3、仿真结果

总结

前言

这里是小白新手的课后作业之——基于FPGA的四选一数据选择器的设计!!

一、四选一多路选择器原理

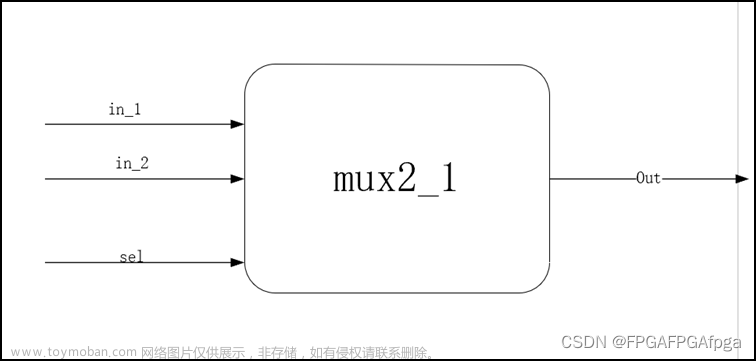

四选一多路选择器共由四个1位的输入端口(int0、int1、int2、int3)、一个2位控制端口(sel)和一个输出端口(out)组成,原理如图1所示,真值表如下:

| sel | out |

|---|---|

| 00 | int0 |

| 01 | int1 |

| 10 | int2 |

| 11 | int3 |

图1

二、原代码

1.Verilog源码

//四位选一多路选择器

// 定义模块名及输入输出变量

module mux4_1 (

input wire [0:0] int0 ,

input wire [0:0] int1 ,

input wire [0:0] int2 ,

input wire [0:0] int3 ,

input wire [1:0] sel ,

output reg [0:0] out

);

//逻辑功能描述

always @(*) begin

case (sel)

2'b00 : out = int0; // sel=0,输出为int0

2'b01 : out = int1; // sel=0,输出为int1

2'b10 : out = int2; // sel=0,输出为int2

2'b11 : out = int3; // sel=0,输出为int3

default : out = 1'bx ; //默认处理输出为空

endcase

end

endmodule2.测试文本

`timescale 1ns/1ns // 定义时间单位和延时精度

module mux4_1_tb(); // 定义模块名

// 定义激励信号

reg tb_int0 ;

reg tb_int1 ;

reg tb_int2 ;

reg tb_int3 ;

reg [1:0] tb_sel ;

// 定义输出信号

wire out;

parameter TIME = 20;

// 模块例化

mux4_1 mux4_1_tb(

.int0 (tb_int0) ,

.int1 (tb_int1) ,

.int2 (tb_int2) ,

.int3 (tb_int3) ,

.sel (tb_sel) ,

.out (out)

);

// 模拟输入

initial begin

tb_int0 = 0; // 将tb_int0初始化为0

forever begin

#TIME;

tb_int0 = ~tb_int0; // 每20个时间单位内,将tb_int0的值取反

end

end

initial begin

tb_int1 = 0; // 将tb_int1初始化为0

forever begin

#(TIME*2);

tb_int1 = ~tb_int1; // 每40个时间单位内,将tb_int1的值取反

end

end

initial begin

tb_int2 = 0; // 将tb_int2初始化为0

forever begin

#(TIME*3);

tb_int2 = ~tb_int2; // 每60个时间单位内,将tb_int2的值取反

end

end

initial begin

tb_int3 = 0; // 将tb_int3初始化为0

forever begin

#(TIME*4);

tb_int3 = ~tb_int3; // 每80个时间单位内,将tb_int3的值取反

end

end

initial begin

tb_sel = 0; // 将tb_sel初始化为0

forever begin

#(TIME*6);

tb_sel = ~tb_sel; // 每160个时间单位内,将tb_sel的值取反

end

end

endmodule3、仿真结果

文章来源:https://www.toymoban.com/news/detail-714124.html

文章来源:https://www.toymoban.com/news/detail-714124.html

总结

咔嚓又是一天文章来源地址https://www.toymoban.com/news/detail-714124.html

到了这里,关于FPGA四选一多路选择器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!