WARNING: [Xicom 50-38] xicom: No CseXsdb register file specified for CseXsdb slave type: 0, cse driver version: 0. Slave initialization skipped.

INFO: [Labtools 27-1434] Device xc7a35t (JTAG device index = 0) is programmed with a design that has no supported debug core(s) in it.文章来源:https://www.toymoban.com/news/detail-714127.html

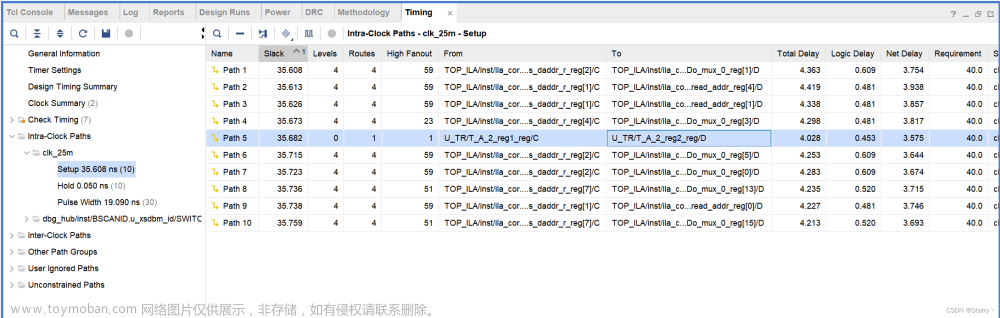

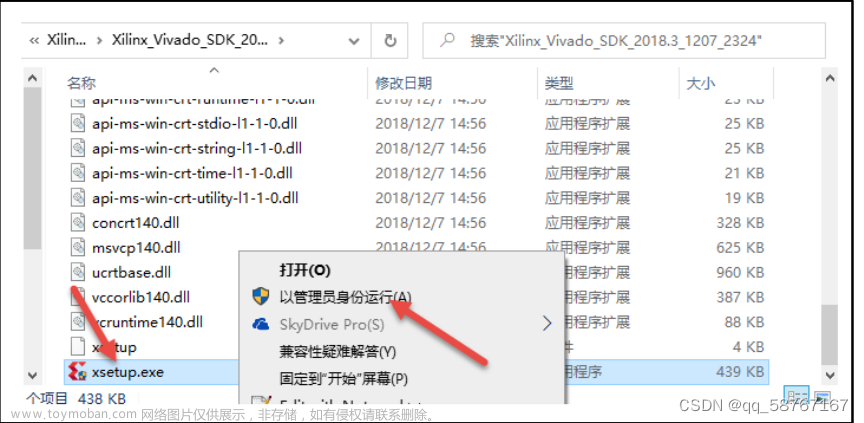

记录一下这个错误,在vivado例化ILA调试波形时,在Hardware界面进行program Device时老是出不来波形调试窗口并且弹出上面的warning,经过调试了昨天一天加上今天看师兄之前的文件终于发现了原因是xdc文件里约束有问题,之前是注释掉的语句,改成现在的样子,重新综合、布局布线、生成bit文件下载到板子上最终成功出现了波形调试界面。 文章来源地址https://www.toymoban.com/news/detail-714127.html

文章来源地址https://www.toymoban.com/news/detail-714127.html

到了这里,关于VIVADO ILA调试的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[VIVADO] 集成逻辑分析仪(ILA)的4种使用方法](https://imgs.yssmx.com/Uploads/2024/02/753842-1.png)