进行综合之后报错,意思是设置的时钟频率超出例化器件的工作频率范围。

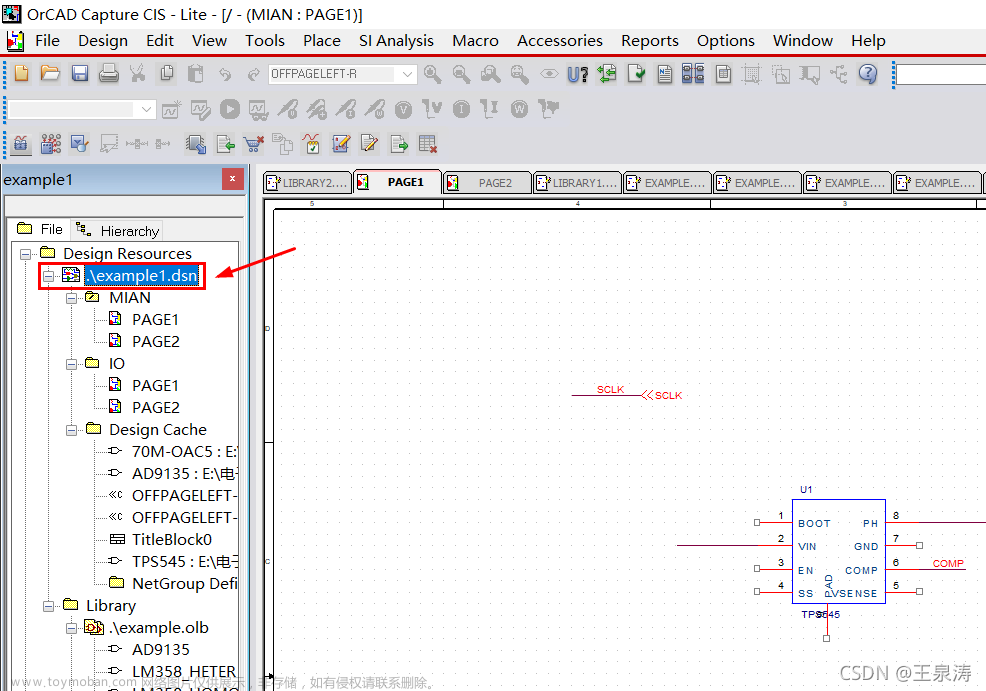

检查之后是PLL的IP核输出端口命名时顺序出错,如下

调整之后,综合通过

文章来源:https://www.toymoban.com/news/detail-714134.html

文章来源:https://www.toymoban.com/news/detail-714134.html

文章来源地址https://www.toymoban.com/news/detail-714134.html

到了这里,关于[DRC PDRC-34] MMCM_adv_ClkFrequency_div_no_dclk: The computed value 96.000 MHz (CLKIN1_PERIOD的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![【常见 error】Vivado生成比特流时报错[DRC NSTD-1]和[DRC UCIO-1]](https://imgs.yssmx.com/Uploads/2024/02/781543-1.png)

![Vivado Error问题之[DRC NSTD-1][DRC UCIO-1] FPGA管脚约束问题导致生成bit时报错,如何在不重新Implentation情况下生成bit?](https://imgs.yssmx.com/Uploads/2024/01/804972-1.png)