目录

1. 认识FPGA

什么是FPGA

FPGA的编程过程

2. 认识ARM

什么是ARM

ARM与FPGA的区别

ARM与Linux

3. 认识ZYNQ

ZYNQ与FPGA的区别

ZYNQ的"ARM"和"FPGA"

关于PL

关于PS

4. 学习用板载资源

5. 总结

1. 认识FPGA

-

什么是FPGA

FPGA是一种集成电路,它可以在制造后由客户或设计者根据需要配置电路功能 。FPGA的内部由可编程逻辑、专用功能块和可编程互连组成。FPGA的结构可以根据不同的厂商和型号有所差异,但一般包括以下几种主要元素:

- 可配置逻辑块(CLB):是FPGA的基本单元,可以实现任意的逻辑功能。每个CLB由一些查找表(LUT)、触发器、多路复用器等组成;

- 数字信号处理(DSP)块:是FPGA的专用功能块之一,可以高效地实现数字信号处理的功能,如滤波、乘法、累加等;

- 收发器(Transceiver):是FPGA的专用功能块之一,可以实现高速的串行数据的发送和接收,支持多种协议和标准;

- 块随机存取存储器(BRAM):是FPGA的专用功能块之一,可以提供片上的存储空间,支持多种访问模式和配置方式;

- 可编程互连:是FPGA的重要组成部分,可以实现不同的CLB和功能块之间的连接和通信,支持多种拓扑结构和路由算法;

FPGA的应用领域非常广泛,主要包括以下几类:

- 通信和网络:FPGA可以实现高速的数据传输和处理功能,支持多种通信协议和标准,如5G、WiFi、Ethernet等;

- 数据中心和云计算:FPGA可以实现高效的数据加密和压缩功能,支持多种云服务和平台,如AWS、Azure等;

- 人工智能和机器学习:FPGA可以实现高性能的神经网络和深度学习功能,支持多种模型和算法,如CNN、RNN等;

- 嵌入式系统和物联网:FPGA可以实现低功耗的智能控制和传感功能,支持多种嵌入式操作系统和物联网协议,如Linux、MQTT等;

- 数字信号处理和图像处理:FPGA可以实现高精度的信号采集和分析功能,支持多种信号处理和图像处理算法,如FFT、DCT、OpenCV等;

- 工业控制和汽车电子:FPGA可以实现高可靠的工业控制和汽车电子功能,支持多种工业总线和汽车标准,如CAN、FlexRay等;

学习FPGA可以提高自己的硬件设计能力和创新能力,可以实现自己的想法和算法,可以解决实际的问题和挑战,可以参与到前沿的技术和项目中;

-

FPGA的编程过程

FPGA编程通过使用硬件描述语言(HDL)或其他工具来定义和配置FPGA上的逻辑电路。FPGA编程的主要步骤包括:

- 硬件架构设计:确定FPGA的输入输出接口,时钟频率,资源利用率等;

- 设计:使用HDL(如VHDL或Verilog)或其他工具(如MATLAB或Simulink)来描述硬件逻辑,实现算法功能;

- 验证:使用仿真或测试平台来检查设计是否符合预期,是否存在错误或缺陷;

- 综合:将HDL代码转换为适合FPGA的逻辑门电路,优化性能和资源消耗;

- 集成:将设计与FPGA的固有资源(如引脚,时钟,ADC等)以及外部设备(如内存,传感器等)进行连接和配置;

- 实现:将综合后的逻辑门电路映射到FPGA的物理资源上,并进行布局和布线,生成可以下载到FPGA的比特流文件;

- 实验测试和调试:将比特流文件下载到FPGA上,并使用真实或测试输入来运行和观察结果,发现并解决问题;

2. 认识ARM

-

什么是ARM

ARM(Acorn RISC Machine)是一家英国的半导体公司,它设计和授权处理器IP,提供了多种性能、功耗和成本需求的处理器。ARM的处理器包括:

- Cortex-A系列:面向性能密集型系统的应用处理器内核;

- Cortex-R系列:面向实时应用的高性能内核;

- Cortex-M系列:面向各类嵌入式应用的微控制器内核;

- Neoverse:满足大型互联网和 HPC高性能计算应用需求的高性能内核;

- Ethos:专门用于加速人工智能和机器学习的神经处理器内核;

- SecurCore:基于Cortex-M3核的高安全性微控制器内核;

ARM的处理器广泛应用于智能手机、平板电脑、物联网设备、云计算、汽车电子、嵌入式系统等领域;

-

ARM与FPGA的区别

ARM与FPGA的区别主要有以下几点:

- ARM的功能主要是执行软件指令,实现数据处理、事务管理、界面显示、应用程序等功能,它可以运行多种操作系统和开发环境,也可以调用多种现成的硬件资源;

- FPGA的功能主要是实现硬件逻辑,实现数据加速、并行处理、信号处理、图像处理等功能,它可以根据不同的需求和设计来配置电路功能,也可以通过添加软核或硬核来实现处理器功能;

- ARM和FPGA的功能可以相互补充,也可以相互竞争,取决于具体的应用场景和性能要求。一般来说,ARM更适合控制类的应用,而FPGA更适合计算类的应用;

-

ARM与Linux

Linux是一种开源的操作系统,可以根据不同的需求和环境来定制和优化,具有灵活性高、兼容性强、稳定性好等特点,适用于多种应用场景,如嵌入式系统、物联网设备、数据中心等。在ARM上运行Linux可以充分利用ARM的处理能力和节能特性,可以提高系统的性能和效率,可以降低系统的成本和功耗,可以增加系统的功能和可扩展性;

在ARM上运行的Linux系统有很多种,例如:

- Arch Linux ARM:基于Arch Linux的分支,提供了一个轻量级、灵活、可定制的Linux系统,支持多种ARM设备;

- Debian ARM:基于Debian的分支,提供了一个稳定、成熟、兼容的Linux系统,支持多种ARM设备;

- Armbian:基于Debian或Ubuntu的分支,专门为ARM开发板定制的Linux系统,提供了优化的性能和稳定性;

- Linux Mint Debian Edition (LMDE):基于Debian Testing的分支,提供了一个友好、美观、功能丰富的Linux系统,支持多种ARM设备;

- Manjaro ARM:基于Manjaro的分支,提供了一个快速、现代、易用的Linux系统,支持多种ARM设备;

- Ubuntu Server ARM:基于Ubuntu Server的分支,提供了一个适用于云计算和边缘计算的Linux系统,支持多种ARM服务器设备;

3. 认识ZYNQ

-

ZYNQ与FPGA的区别

ZYNQ(zynq-7000 All Programmable SoC)是Xilinx推出的新一代全新可编程片上系统,在传统FPGA芯片的基础上集成了1-2个ARM处理器,同时具备了软件可编程和硬件可编程的特性,将ARM的控制能力和FPGA的计算性能完美结合,提供无与伦比的系统性能、灵活性和可扩展性;

ZYNQ与FPGA的区别主要有以下几点:

- ZYNQ相比FPGA,具有更强的处理能力和灵活性,可以利用ARM处理器实现复杂的软件功能和控制逻辑,也可以利用可编程逻辑实现硬件加速和算法优化;

- FPGA相比ZYNQ,具有更高的自由度和定制性,可以根据不同的需求和设计来配置电路功能,也可以通过添加软核或硬核来实现处理器功能;

除此之外,ZYNQ内部ARM部分和FPGA部分的完美结合,是普通FPGA无法做到的;

-

ZYNQ的"ARM"和"FPGA"

ZYNQ具备ARM Cortex-A9内核和28nm Artix 7 FPGA结构,在ZYNQ片内被称为PS和PL:

- PS(Processing System)是指处理系统,它包括双核ARM Cortex-A9处理器和一系列的片上外设,如内存控制器、DMA控制器、USB控制器、以太网控制器等;

- PL(Programmable Logic)是指可编程逻辑,它包括基于Artix-7或Kintex-7的可编程逻辑单元,如可配置逻辑块、DSP块、BRAM块等;

- ZYNQ的PS和PL之间通过多种AXI接口进行连接和通信,可以实现软硬件协同设计,提高系统的性能和灵活性;

PL和PS虽是ZYNQ片内的两个主要部分,但二者既可以协同工作,又可以独立工作;

-

关于PL

了解PL首先要了解什么是PLD,早期生产的数字集成电路逻辑功能都是固定不变的。要想改变它的逻辑功能,就必须改变内部各单元电路之间的连接,而这种连接在集成电路制作过程中已经固定下来了。

为了提高灵活性,出现了允许用户自行修改内部连接的集成电路:可编程逻辑器件PLD(Programmable Logic Device)

- PLD内部的电路结构可以通过写入编程数据来设置;

- 写入PLD的编程数据还可以擦除重写;

FPGA是一种PLD,除FPGA(现场可编程门阵列)外,CPLD(复杂可编程逻辑器件)也属于PLD,二者的本质区别是:

- CPLD:基于“乘积项”的与或逻辑阵列;

- FPGA:基于“查找表”(LUT,Look UP Table)的CLB阵列;

PL与FPGA的结构相同

图1 FPGA架构

FPGA的架构是指FPGA内部的组成和连接方式,它决定了FPGA的功能和性能。根据图1,FPGA的基本架构包括以下几个部分:

- 可编程IO单元(I/O):这些物理端口将数据输入和输出FPGA,可以根据不同的信号标准和电压水平进行配置;

- 可编程逻辑单元(LC):这些是执行逻辑运算的基本单元,通常由查找表(LUT)、触发器(FF)和多路复用器等组成。LUT可以存储任意的逻辑函数,FF可以存储LUT的结果。不同的FPGA有不同数量和类型的输入的LUT,如输入LUT、输入LUT等;

- 布线资源:这些是将各种元件彼此连接的导线和开关,可以实现不同的信号路径。布线资源的数量和质量影响了FPGA的逻辑密度和时序性能。

- 嵌入式块式 RAM(BRAM):这些是用于存储数据的内存模块,可以配置为不同的位宽和深度,也可以级联成更大的内存空间。BRAM可以提供高速、低功耗、低延迟的数据访问。

- 数字时钟管理模块(CMT):这些是用于产生、分配和调整时钟信号的模块,包括相位锁定环(PLL)、延迟锁定环(DLL)、时钟缓冲器等。CMT可以提供多种频率和相位的时钟信号,实现时钟域之间的转换和同步。

- 内嵌专用硬核:这些是用于实现特定功能的硬件模块,如乘法器、累加器、DSP切片、PCI Express接口等。内嵌专用硬核可以提高FPGA的计算能力和接口兼容性,降低逻辑资源和功耗的消耗。

- 底层内嵌功能单元:这些是用于实现一些底层功能的单元,如配置逻辑、JTAG接口、电源管理等。底层内嵌功能单元可以保证FPGA的正常工作和可靠性。

ZYNQ系列的PL结构如图2所示,可以与FPGA的结构进行对照;

图2 ZYNQ的PL结构

ZYNQ7010和7020都使用了Artix-7的结构,可以看到,除了基本的结构,ZYNQ系列的PL还具备了如GTX transceiver和PCIE等独特结构,但ZYNQ7010和7020不包含这些结构;

-

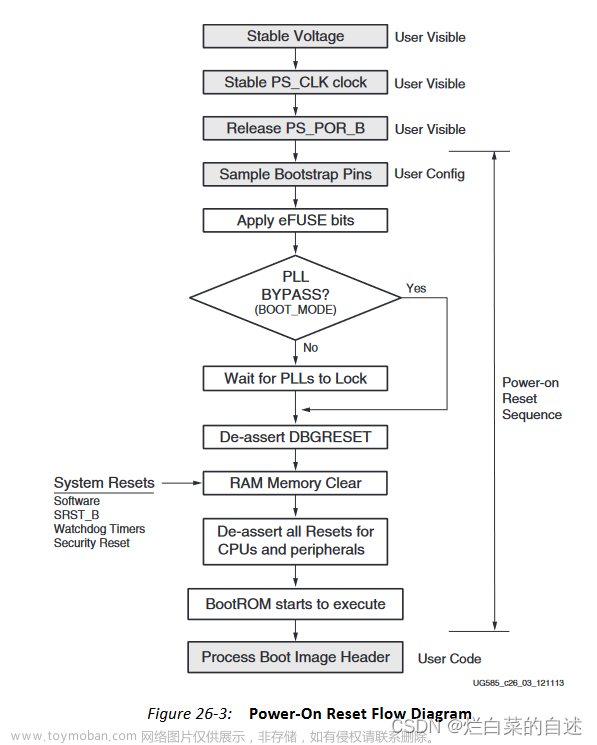

关于PS

PL与PS在片内的结构如图3所示,可以看到两个结构基本是分开的

图3 PL和PS的片内结构

PS最重要的部分是图3中的应用处理单元APU(Application Processing Unit),如图4所示

图4 APU结构

可以看到,APU内部不仅有Cortex-A9内核,还包含了FPU浮点运算单元,NEON SIMD (Single Instruction Multiple Data 单指令多重数据) 指令集,MMU存储管理单元,一级cache(I代表指令cache,D代表数据cache),窥探控制单元SCU(Snoop Controller),私有看门狗AWDT,定时器TIMER,二级cache(双核公用),片上内存OCM,中断控制器GIC,直接存储器访问DMA等;

PS内部APU外部,结合图片分析,就可以理解APU与外部的连接方式,比较重要的是Central interconnect模块,负责控制APU与各模块之间的连接,除控制通信接口,还包含了对动态存储器访问(DDR3)和静态存储器(QSPI Flash)访问;

PS连接外部,结合图片分析,PS与PL的连接,GP接口(General-Purpose Port),HP接口(High-Performance Ports)和ACP(Accelerator Coherency Port)都属于AXI片内通信协议,图5描述了GP接口和ACP的结构

图5 GP接口的结构

由图5看出,ACP用于访问SCU实现PL和PS二级cache与SRAM的高速存取,GP接口用于通用的PL和PS通信,并且区分M(Master)和S(Slave)通信机制,HP接口用于高速通信,并且通信自带FIFO,连接在存储仲裁器(memory interconnect),可用于访问DDR3,适合大量数据流传输;

| 接口名称 | 接口描述 | 主设备 | 从设备 |

| M_AXI_GP0 | 通用接口(AXI_GP) | PS | PL |

| M_AXI_GP1 | PS | PL | |

| S_AXI_GP1 | 通用接口(AXI_GP) | PL | PS |

| S_AXI_GP1 | PL | PS | |

| M_AXI_ACP | ACP 缓存(cache)一致性传输 | PL | PS |

| M_AXI_HP1 | 带有读写FIFO的高速接口(需要注意HP有时被称为AXI FIFO interface[AXI FIFO接口],或者AFIs) | PL | PS |

| M_AXI_HP1 | PL | PS | |

| S_AXI_HP1 | PL | PS | |

| S_AXI_HP1 | PL | PS |

AXI是高级微控制器总线架构(AMBA3.0/4.0)的一部分,全称高级扩展接口(Advanced Extensible Interface),ZYNQ使用的是AMBA4.0标准中的AXI-4,分为memory map,stream和lite三种,如图6所示;

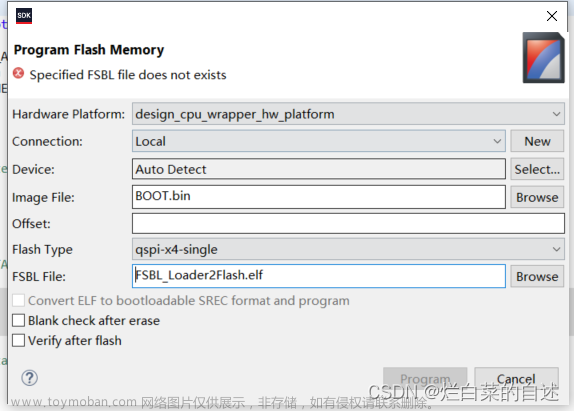

图6 AMBA与AXI

除了AXI接口之外,还包含了IO拓展EMIO,XADC(来自PL硬核),DMA,IRQ,AEX/SHA配置(此配置用于PS配置PL的启动,代表了PS和PL不是完全独立的,ZYNQ整个设计是以ARM处理器为中心的,PS端的ARM内核可以独立于PL端运行,值得注意的是,虽然PL端也可以独立于PS端运行,但是PL的配置是由PS端完成的,所以不能采用传统的固化FLASH的方式固化PL端程序)等连接;

4. 学习用板载资源

- 主芯片 ZYNQxc7z010 677M(-1) 28k Programmable Logic Cells

- 512MB DDR3 (4Gbit)

- TF卡槽(可负责TF启动)

- 128Mbit(16MB)QSPI FLASH(可负责启动)

- 一路EEPROM 2KB (PS)

- 两路 LED 灯(PL)

- 两个按键 (PL) +一个控制系统POR复位的按键

- 一路UART(PS)

- 一路板载XILINX 下载器 JTAG

- 一路USB 可作USB SLAVE 或USB HOST

- 引出 68路GPIO

- 千兆以太网(PL)

- HDMI 输出接口 支持1080P 60hz

- 1.47寸 彩色LCD 显示屏 172X320 (PL)

- 50M有源晶振(PL)

5. 总结

笔记对应课程:文章来源:https://www.toymoban.com/news/detail-714137.html

- 第1.1讲 ZYNQ简介(第一讲)

- 第1.2讲 ZYNQ简介(第二讲)

图片来自正点原子课程PPT,笔记中有自己理解的内容,如有错误,欢迎指正文章来源地址https://www.toymoban.com/news/detail-714137.html

到了这里,关于从零开始学ZYNQ(FPGA)笔记二 | 认识学习内容的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!