【2022.04西南交大数电实验】

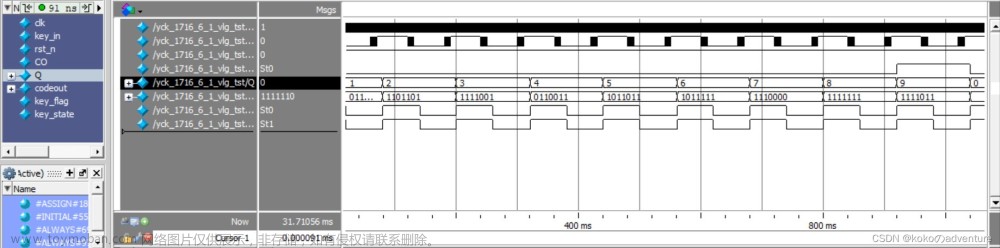

module yck_1716_2(codeout,clk,en,Q);

input clk,en;

output [2: 0] Q;

output [6: 0] codeout;

yck_1716_2_1 a(clk,en,Q);

yck_1716_2_2 b(codeout, Q);

endmodule

module yck_1716_2_1(clk,en,Q);

input clk,en;

output reg[2:0] Q;

always@(posedge clk)

begin

if(en == 1'b1)

begin

if(Q < 3'd6)

Q <= Q + 1'b1;

else

Q <= 0;

end

else

Q <=Q;

end

endmodule

module yck_1716_2_2(codeout, Q);

input[2: 0] Q;

output reg[6: 0] codeout;

always @ (*) //用always块语句描述逻辑

begin

case (Q)

3'd0: codeout <= 7'b0000001;

3'd1: codeout <= 7'b0000011;

3'd2: codeout <= 7'b0000111;

3'd3: codeout <= 7'b0001111;

3'd4: codeout <= 7'b0011111;

3'd5: codeout <= 7'b0111111;

3'd6: codeout <= 7'b0000000;

default: codeout <= 7'bx;

endcase

end

endmodule

文章来源:https://www.toymoban.com/news/detail-714581.html

文章来源:https://www.toymoban.com/news/detail-714581.html

文章来源地址https://www.toymoban.com/news/detail-714581.html

文章来源地址https://www.toymoban.com/news/detail-714581.html

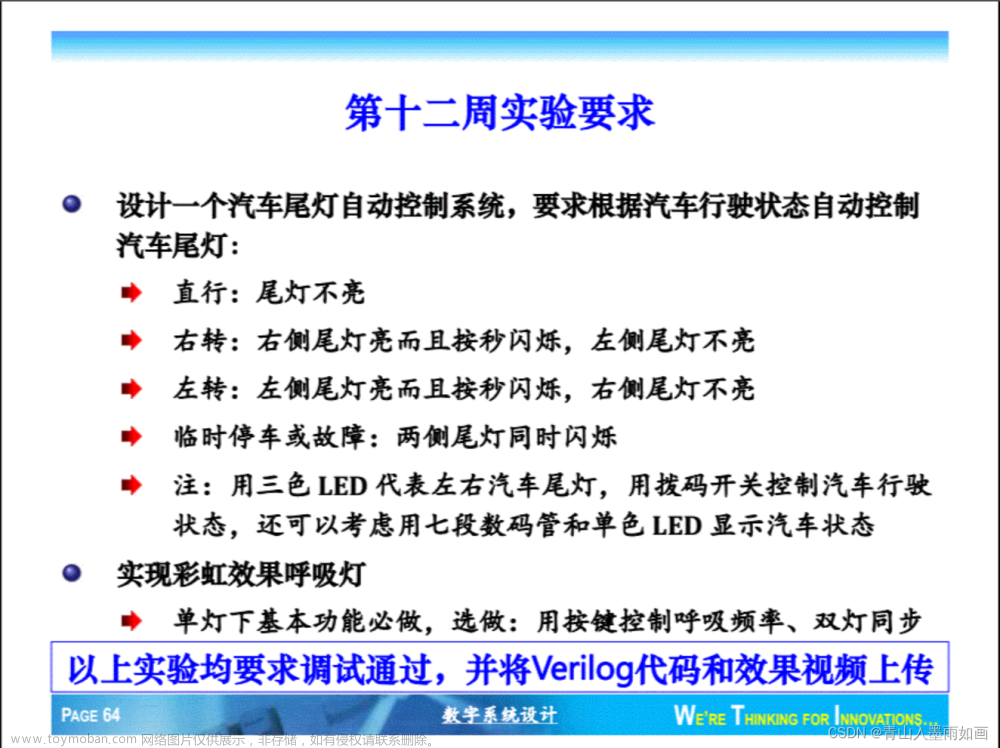

到了这里,关于【数电实验2】Verilog—汽车流动转向灯电路设计(层次化文件设计)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!