请阅读【嵌入式开发学习必备专栏 】

1. ARM Coresight SoC-400/SoC-600 专栏导读目录

1.1 ARM Coresight 专题

本专栏全面介绍 ARM Coresight 系统 及SoC-400, SoC-600 中的各个组件。

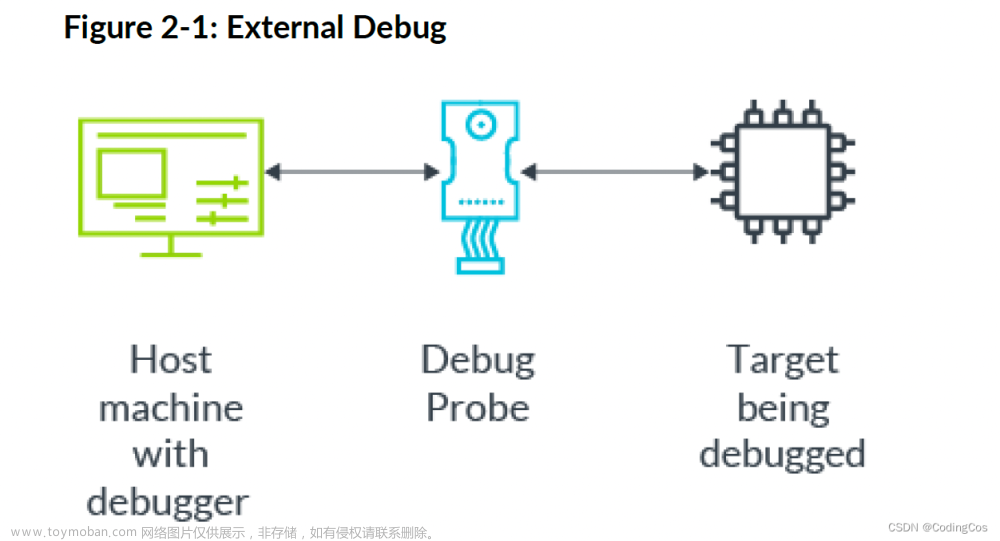

- 【ARM Coresight Debug 系列 1 – ARM Debug 技术概述】

- 【ARM Coresight 系列文章 2 - ARM Coresight 介绍】

- 【ARM Coresight 系列文章 2 - ARM Coresight 介绍】

- 【ARM Coresight 系列文章 2.1 - ARM Coresight 组件分类及功能介绍】

- 【ARM Coresight 系列文章 2.2- ATB 总线简介】

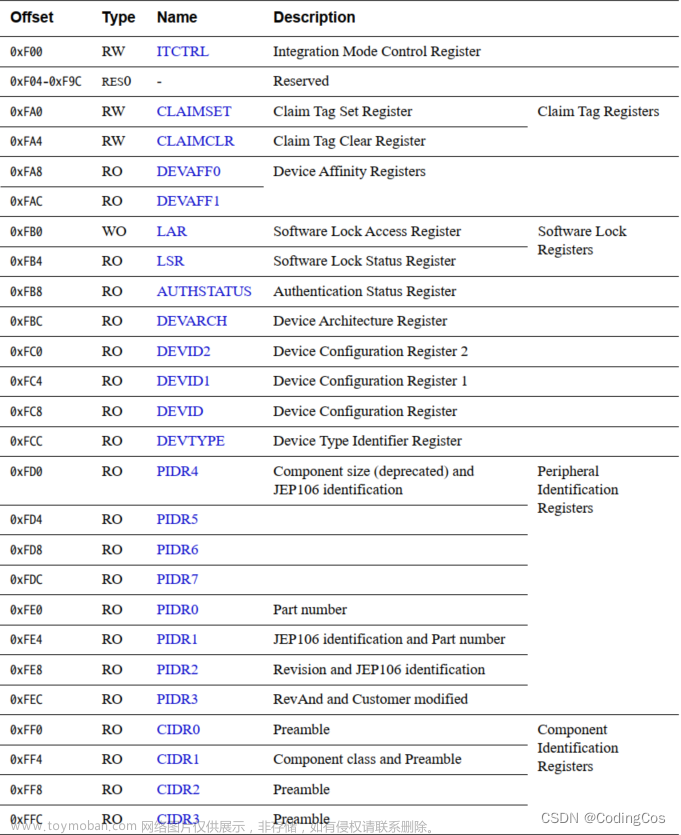

- 【ARM Coresight 系列文章 2.3 - Coresight 寄存器】

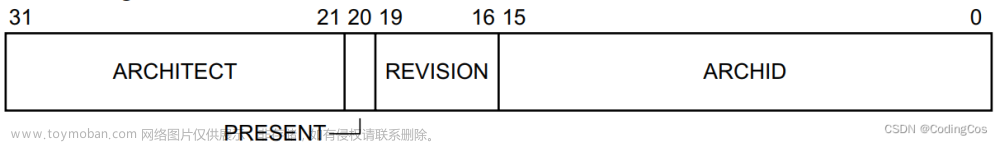

- 【ARM Coresight 系列文章 2.4 - Coresight 寄存器:DEVARCH,DEVID, DEVTYPE】

- 【ARM Coresight 系列文章 2.5 - Coresight 寄存器:PIDR0-PIDR7,CIDR0-CIDR3 介绍】

- 【ARM Coresight 系列文章 3 – DAP(Debug Access Port) 使用详细介绍】

- 【ARM Coresight 系列文章 3.1 - ARM Coresight DP 对 AP 的访问 1】

- 【ARM Coresight 系列文章 3.2 - ARM Coresight DP 对 AP 的访问 2】

- 【ARM Coresight 系列文章 3.3 - ARM Coresight SWD 协议详细介绍】

- 【ARM Coresight 系列文章 3.4 - ARM Coresight JTAG 详细介绍】

- 【ARM Coresight 系列文章 3.5 - ARM Coresight – JTAG-DP(JTAG Debug Port) 详细介绍】

- 【ARM Coresight 系列文章 4 - ARM Coresight APB-AP 介绍】

- 【ARM Coresight 系列文章 5 - ARM Coresight APB Interconnect(APBIC)】

- 【ARM Coresight 系列文章 6 - ARM Coresight ROM Table】

- 【ARM Coresight 系列文章 7 - ARM Coresight 通过 AHB-AP 访问 cpu 内部 coresight 组件】

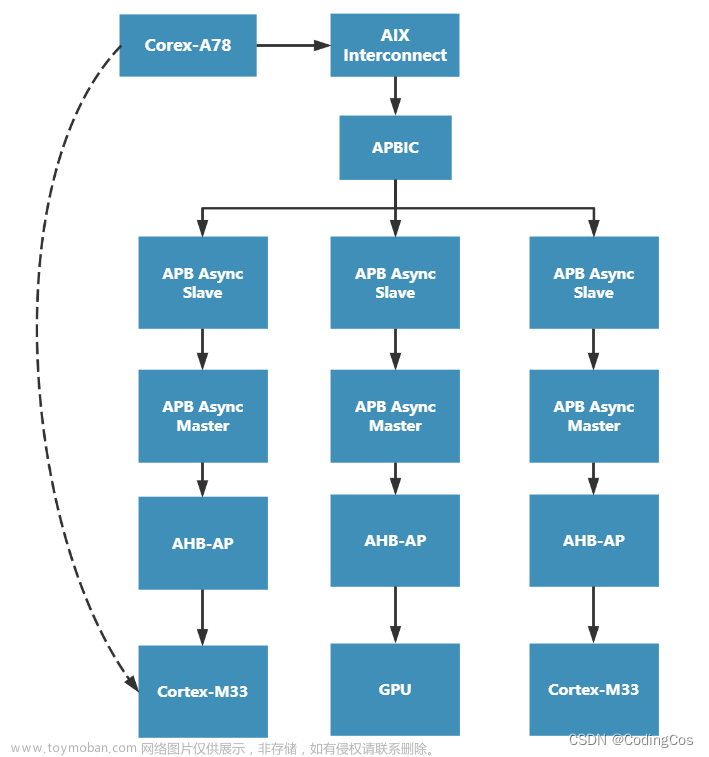

- 【ARM Coresight 系列文章 8 - ARM Coresight 通过 APBIC 级联使用】

- 【ARM Coresight 系列文章 9 – ETM(Embedded Trace Macrocell) 详细介绍 】

- 【ARM Coresight 系列文章 10 - ARM Coresight STM 介绍及使用】

- 【ARM Coresight 系列文章 10.1 - ARM Coresight STM 介绍及使用】

- 【ARM Coresight 系列文章 10.2 - ARM Coresight STM Trace packets】

- 【ARM Coresight 系列文章 10.3 - ARM Coresight STM 寄存器介绍 及STM DMA 传输介绍】

- 【ARM Coresight 系列文章 11 – CoreSight ECT(Embedded Cross Trigger)and CTI】

- 【ARM Coresight 系列文章 12 - ARM Coresight ELA-500】

- 【ARM Coresight 系列文章 13 – 格雷码(Gray Code)与 coresight timestamp】

- 【ARM Coresight 系列文章 14 - Cortex-M DWT 详细介绍】

- 【ARM Coresight 系列文章 15 – SoC-400 介绍 】

- 【ARM Coresight 系列文章 15.1 – Granular Power Requester 】

- 【ARM Coresight 系列文章 15.2 – components power domain 详细介绍】

- 【ARM Coresight Debug 系列 16 – Linux 断点 BRK 中断使用详细介绍】

- 【ARM Coresight Debug 系列 17 – ARM Debug Vector Catch 详细介绍】

1.1.1 Performance Profiling

- 【ARM Coresight 系列文章19 – Performance Monitoring Unit(性能监测单元)

- 【ARM Coresight 系列文章19.1 – Cortex-A720 PMU 详细介绍】

- 【ARM Coresight 系列文章19.2 – Cortex-A720 AMU 详细介绍】

- 【ARM Coresight 系列文章 20 – linux perf 与 ARM coresight】

- 【ARM Coresight 系列文章 20.1 – linux perf event 的注册】

1.1.2 ARM Coresight Debug 工具系列

1.1.2.1 ARM DS5 系列

- 【ARM Coresight 系列文章 1 - ARM DS-5 介绍】

- 【ARM Coresight DS-5 系列 1.1 - ARM Cortex-M DS-5 使用配置】

- 【ARM Coresight DS-5 系列 2 - ARM Cortex-M DS-5 Trace 使用】

- 【ARM Coresight DS-5 系列 3 - DS-5 断点设置及常用Debug 命令】

- 【ARM Coresight DS-5 系列 4 - ARM Cortex-M DS-5 加载 ELF 文件运行】

1.1.2.2 劳特巴赫 Trace32 系列

- 【ARM Trace32(劳特巴赫) 使用介绍 1 - Veloce 环境中使用 Trace32】

- 【ARM Trace32(劳特巴赫) 使用介绍 1.1 - Veloce 环境中使用trace32 连接 Cortex-M33】

- 【ARM Trace32(劳特巴赫) 使用介绍 1.2 - ARM 系统调试中常见的挑战】

- 【ARM Trace32(劳特巴赫) 使用介绍 2 - Veloce 环境中使用trace32 连接 Cortex-M33】

- 【ARM Trace32(劳特巴赫) 使用介绍 2.1 – TRACE32 Practice 脚本 cmm 脚本学习】

- 【ARM Trace32(劳特巴赫) 使用介绍 2.2 – TRACE32 进阶命令之 DIAG 弹框命令】

- 【ARM Trace32(劳特巴赫) 使用介绍 2.3 – TRACE32 进阶命令之 参数传递介绍】

- 【ARM Trace32(劳特巴赫) 使用介绍 2.4 – TRACE32 进阶命令之 CPU 运行状态检查命令 state.run】

- 【ARM Trace32(劳特巴赫) 使用介绍 3 - trace32 访问运行时的内存】

- 【ARM Trace32(劳特巴赫) 使用介绍 3.1 – 不 attach core 直接访问 memory】

- 【ARM Trace32(劳特巴赫) 使用介绍 4 - Trace32 Discovery 详细介绍】

- 【ARM Trace32(劳特巴赫) 使用介绍 5 – Trace32 ELF 文件加载介绍】

- 【ARM Trace32(劳特巴赫) 使用介绍 6 – 通用寄存器查看与修改】

- 【ARM Trace32(劳特巴赫) 使用介绍 6.1 – 外设寄存器查看与修改】

- 【ARM Trace32(劳特巴赫) 使用介绍 9 – Trace32 通过 JTAG 命令获取数据寄存器 IDCODE的值】

- 【ARM Trace32(劳特巴赫) 使用介绍 10 – Trace32 scan dump 详细介绍】

- 【ARM Trace32(劳特巴赫) 使用介绍 11 – Trace32 ARMv8/v9 系统寄存器读写】

- 【ARM Trace32(劳特巴赫) 使用介绍 12 – Trace32 常用命令之 d.dump | data.dump 介绍】

- 【ARM Trace32(劳特巴赫) 使用介绍 13 – Trace32 Var 变量篇】

- 【ARM Trace32(劳特巴赫) 使用介绍 13.1 – Trace32 Var 变量篇 – 符号表】

- 【ARM Trace32(劳特巴赫) 使用介绍 13.2 – Trace32 断点 Break 命令篇】

- 【ARM Trace32(劳特巴赫) 使用介绍 14 – Go.direct 介绍】

- 【ARM Trace32(劳特巴赫) 高级篇 20 – SNOOPer 使用介绍】

- 【ARM Trace32(劳特巴赫) 高级篇 20.1 – SNOOPer 变量采样】

- 【ARM Trace32(劳特巴赫) 高级篇 21 – Trace 系统性能分析 Performance Analyzer】

1.1.2.3 JTAG OpenOCD 系列

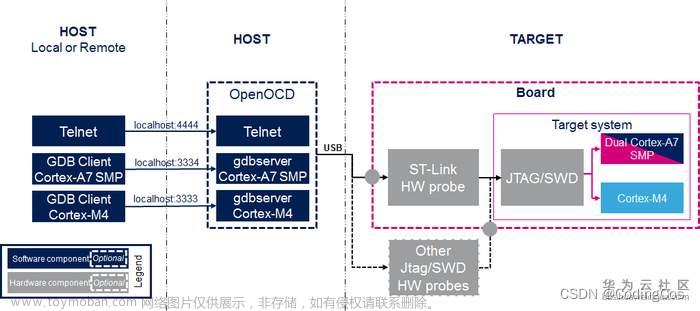

- 【ARM Coresight OpenOCD 系列 1 – OpenOCD 介绍】

- 【ARM Coresight OpenOCD 系列 2 – OpenOCD 脚本语法详细介绍】

1.2 ARM Cache 专题

- 【ARM Cache 系列文章 1 – Cache基础概念学习】

- 【ARM Cache 系列文章 2 – Cache Coherence及内存顺序模学习】

- 【ARM Cache 系列文章 3 – Cache 与 MPU关系学习】

- 【ARM Cache 系列文章 4 – Cache 与 CPU 乱序执行】

- 【ARM Cache 系列文章 5 – 内存屏障ISB/DSB/DMB】

- 【ARM Cache 系列文章 6 番外篇 – MMU, MPU, SMMU, PMU 差异与关系】

- 【ARM Cache 系列文章 7 – ARMv8/v9 MMU 页表配置 01 】

- 【ARM Cache 系列文章 8 – ARM DynamIQ 技术介绍】

- 【ARM Cache 系列文章 9 番外篇 – ARMv9 Core 介绍】

- 【ARM Cache 系列文章 10 – 缓存一致性协议】

- 【ARM Cache 系列文章 11 – ARM Cortex-A720 Hunter 介绍】

1.3 ARM AMBA Bus

1.3.1 AMBA AXI 系列

- 【ARM AMBA AXI 入门 1 – AXI 握手协议入门】

- 【ARM AMBA AXI 入门 2 - AXI协议中的 BURST Transfer】

- 【ARM AMBA AXI 入门 3 - AXI 协议中的 Outstanding transfer 】

- 【ARM AMBA AXI 入门 4 - AXI 协议中的 Out-of-Order transfer and interleave 介绍 】

- 【ARM AMBA AXI 入门 5 - AXI 协议中的 QoS信号及User信号介绍 】

- 【ARM AMBA AXI 入门 6 - AXI3 协议中的锁定访问之AxLOCK信号】

- 【ARM AMBA AXI 入门 7 - AXI 协议中的独占访问 使用背景介绍】

- 【ARM AMBA AXI 入门 8 - AXI 协议中 RID/ARID/AWID/WID 信号】

- 【ARM AMBA AXI 入门 9 - AXI 总线 AxPROT 与安全之间的关系 】

- 【ARM AMBA AXI 入门 10 - AXI 总线 DATA信号与 STRB 信号之间的关系 】

- 【ARM AMBA AXI 入门 11 - AXI 总线 AWCACHE 和 ARCACHE 介绍】

- 【ARM AMBA AXI 入门 12 – AXI 协议中的 WLAST 与 RLAST】

- 【ARM AMBA AXI 入门 13 – AXI 协议中 RRESP 信号详细介绍】

- 【ARM AMBA AXI 入门 14 - AXI 窄位传输 | 非对齐传输| 大小端传输】

- 【ARM AMBA AXI 入门 15 – AXI-Lite 详细介绍】

- 【ARM AMBA AXI 入门 16 - AXI 写响应通道 BVALID | BREADY | BRESP 详细介绍】

1.3.1 AMBA CHI 系列

- 【ARM AMBA5 CHI 1 – CHI 基础学习 】

- 【ARM AMBA5 CHI 2 – CHI 链路层详细介绍 】

- 【ARM AMBA5 CHI 3 – CHI 协议层详细介绍 】

1.3.2 AMBA APB 系列

- 【ARM AMBA APB 入门 1 – APB总线介绍】

1.3.3 AMBA Power 系列

- 【ARM AMBA Q_Channel 详细介绍】

1.4 ARM CoreLink 系列

- 【ARM CoreLink 系列 1 – SoC 片上互联介绍】

- 【ARM CoreLink 系列 1.1 – CoreLink 系列 产品介绍】

- 【ARM CoreLink 系列 2 – CCI-400 控制器简介】

- 【ARM CoreLink 系列 3 – CCI-550 控制器介绍 】

- 【ARM CoreLink 系列 3.1 – CCI-500 详细介绍 -上半部】

- 【ARM CoreLink 系列 3.2 – CCI-400,CCI-500, CCI-550 差异】

- 【ARM CoreLink 系列 4 – NIC-400 控制器详细介绍】

- 【ARM CoreLink 系列 5 – CI-700 控制器介绍 】

- 【ARM CoreLink 系列 6 – DMC-400控制器简介】

- 【ARM CoreLink 系列 7 – TZC-400控制器简介】

- 【ARM CoreLink 系列 8 – SMMU 详细介绍-上半部】

1.5 ARM 系统稳定性分析系列

1.5.1 Linux 系统稳定性分析

- 【ARM Linux 系统稳定性分析入门及渐进 1 – Crash 工具简介】

- 【ARM Linux 系统稳定性分析入门及渐进 2 – Kernel Lockup】

- 【ARM Linux 系统稳定性分析入门及渐进 3 – 栈溢出】

- 【ARM Linux 系统稳定性分析入门及渐进 4 – 栈分类】

- 【ARM Linux 系统稳定性分析入门及渐进 5 – kernel hung task 工作原理】

1.5.2 GDB 使用系列

- 【ARM Linux 系统稳定性分析入门及渐进10 – GDB 初始化脚本介绍及使用】

- 【ARM Linux 系统稳定性分析入门及渐进11 – GDB( print 和 p 的使用| @ 和 ::的使用|ptype|{<type>} <addr> )】

- 【ARM Linux 系统稳定性分析入门及渐进12 – GDB内存查看命令 “x“(examine)】

- 【ARM Linux 系统稳定性分析入门及渐进 13 – gdb 反汇编 disassemble 命令详细介绍及举例】

1.5.3 RT-Thread 系列

- 【ARM RT-Thread 系统稳定性分析入门及渐进 1 – ASSERT(0) 流程跟踪】

2. ARM GCC 编译专栏

2.1 ARM GCC 编译专栏

- 【ARM 嵌入式编译系列 1 – GNU/GCC/GDB/GNU binutils介绍】

- 【ARM 嵌入式 编译系列 2 – GCC 编译过程介绍】

- 【ARM 嵌入式 编译系列 2.1 – GCC 编译参数学习】

- 【ARM 嵌入式 编译系列 2.2 – 如何在Makefile 中添加编译时间 | 编译作者| 编译 git id】

- 【ARM 嵌入式编译系列 3 – GCC attribute((weak)) 弱符号使用】

- 【ARM 嵌入式 编译系列 3.1 – GCC attribute((used)) 使用】

- 【ARM 嵌入式 编译系列 3.2 – glibc 学习】

- 【ARM 嵌入式 编译系列 3.3 – gcc 动态库与静态库的链接方法介绍】

- 【ARM 嵌入式 编译系列 4 – GCC 编译属性 __read_mostly 详细介绍】

- 【ARM 嵌入式 编译系列 4.1 – GCC 编译属性 likely与unlikely 学习】

- 【ARM 嵌入式 编译系列 4.2 – GCC 链接规范 extern “C“ 介绍】

- 【ARM 嵌入式 编译系列 5 – GCC 内建函数 __builtin 详细介绍】

- 【ARM 嵌入式 编译系列 6 – GCC objcopy, objdump, readelf, nm 介绍】

- 【ARM 嵌入式 编译系列 7 – ARM GCC 链接脚本详细讲解】

- 【ARM 嵌入式 编译系列 7.1 – GCC 链接脚本中节区及各个段的详细介绍】

- 【ARM 嵌入式 番外篇 编译系列 8 – RT-Thread 编译命令 gcc Scons 详细讲解】

- 【ARM 嵌入式 编译系列 9-- GCC 编译符号表(Symbol Table)的详细介绍】

- 【ARM 嵌入式 编译系列 10 – GCC 编译缩减可执行文件 elf 文件大小】

- 【ARM 嵌入式 编译系列 10.1 – GCC 编译缩减可执行文件 elf 文件大小】

- 【ARM 嵌入式 编译系列 10.2 – 符号表与可执行程序分离详细讲解】

- 【ARM 嵌入式 编译系列 10.3 – GNU elfutils 工具小结】

- 【ARM 嵌入式 编译系列 11 – GCC attribute((packed))详细介绍】

- 【ARM 嵌入式 编译系列 11.1 – GCC attribute((aligned(x)))详细介绍】

- 【ARM 嵌入式 编译系列 11.2 – GCC attribute((aligned(x)))详细介绍】

- 【ARM 嵌入式 编译系列 11.3 – GCC attribute packed noreturn constructor 介绍】

—> GCC 编译专栏 <—文章来源:https://www.toymoban.com/news/detail-714739.html

2.1 Makefile 学习

【ARM 嵌入式 编译 Makefile 系列 1 - Makefile 如何调用 shell 脚本】

【ARM 嵌入式 编译 Makefile 系列 2 - Makefile 如何打印信息】

【ARM 嵌入式 编译 Makefile 系列 2.1 - Makefile info,warn, error 打印详细介绍】

【ARM 嵌入式 编译 Makefile 系列 3 - Makefile filter 与 filter-out 详细介绍】

【ARM 嵌入式 编译 Makefile 系列 4 - Makefile函数调用 call 命令详细介绍】

【ARM 嵌入式 编译 Makefile 系列 5 - Makefile函数调用patsubst命令详细介绍】

【ARM 嵌入式 编译 Makefile 系列 6 - Makefile函数调用 origin 命令详细介绍】

【ARM 嵌入式 编译 Makefile 系列 7 - Makefile函数调用 findstring命令详细介绍】

【ARM 嵌入式 编译 Makefile 系列 8 - Makefile函数调用 ifeq 和 ifneq 条件指令详细介绍】

【ARM 嵌入式 编译 Makefile 系列 9 - Makefile “:=”,“ +=”, “?=”,“=” 详细介绍】

【ARM 嵌入式 编译 Makefile 系列 10 - Makefile sort 函数详细介绍】

【ARM 嵌入式 编译 Makefile 系列 11 - Makefile subst 函数详细介绍】

【ARM 嵌入式 编译 Makefile 系列 12 - Makefile notdir 函数详细介绍】

【ARM 嵌入式 编译 Makefile 系列 13 - Makefile eval 函数详细介绍】

【ARM 嵌入式 编译 Makefile 系列 14 - Makefile abspath 函数详细介绍】

【ARM 嵌入式 编译 Makefile 系列 15 - Makefile 标签(targets) 使用详细介绍】

【ARM 嵌入式 编译 Makefile 系列 16 - Makefile 伪目标.PHONY 与 FORCE 详细介绍】

继续更新中…

—> GCC Makefile 编译专栏 <—文章来源地址https://www.toymoban.com/news/detail-714739.html

到了这里,关于【ARM Coresight SoC-400/SoC-600 专栏导读】的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!