目录

一,MOESI状态释义

二,MOESI状态转换

1, Invalid after Reset

2, Invalid => Exclusive

3, Exclusive => Modified

4.1, Modified => Owned, Invalid => Shared

4.2 Modified => Invalid , Invalid => Modified

5,Owned => Invalid, Shared => Invalid, Shared => Modified

6,Clean 和Invalidate操作对MOESI状态的影响

6.1 对 Owned状态进行clean & Invalidate

6.1 对 Shared状态进行clean & Invalidate

三,注意事项

一,MOESI状态释义

ARMv8架构使用 MOESI 协议来维护在多个core之间的数据一致性,MOESI 协议描述了 L1 Data Cache中的一个共享的cache line的状态可以是:

- M,Modified, Unique Dirty, 只存在于当前cache中(unique),并且该cache line上的数据与下一级存储单元中的数据不同(dirty)。换言之,cache line中最新的数据位于当前cache,其他cache中没有备份 ,cache line中的内容与主存中的不一致。

- O,Owned,Shared Dirty,描述一个cache line为dirty,并且可能存在于多个cache中(不止一个)。一个 Owned 状态的cache line保存着 最新的 而且 正确的(new and correct) 的数据。只有一个core的cache 可以将数据保存为 Owned 状态,其他core 为 shared 状态。

- E,Exclusive, Unique Clean,数据只存在于当前cache line中,并且为clean的。cache中cache line中的数据于主存中的一致,并且其他core中的cache没有该地址的数据 备份,只存在一个cache中。

- S,Shared, Shared ,cache line中的data不一定与主存中的一致,与 Owned状态的cache line相对应,将Owned里的数据复制到shared的cache line中,因此 shared cache line中的数据也是最新的。

- I,Invalid,无效的数据。

Data Cache Unit (DCU)会将cache line的 MOESI状态信息保存在tag RAM和 dirty RAM中。

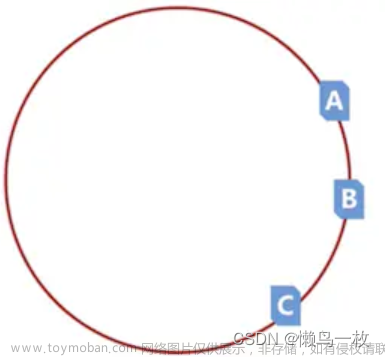

二,MOESI状态转换

下图为MOESI协议的状态转换图。

接下来,本文将结合一个状态转换用例来解释具体的MOESI状态转换。

1, Invalid after Reset

假设当前系统有四个core,每个core有自己独立的data cache,在系统上电后,所有core的cache line都为 invalid状态:

2, Invalid => Exclusive

然后core0 试图读取 内存中地址为 0x44013F00上的数据,core0 的cache中,与该地址相关的cache line的状态将由Invalid 转为 VE,其中V 为Valid,表明该cacheline中的数据有效。E为Exclusive, 表明该数据只在core0中。

3, Exclusive => Modified

之后,core0试图对该地址写入一个新值,该cache line的状态将由VE会变成VDM,其中V为,valid,D为Dirty,表示数据为脏,当前cache line中的数据与主存中的不一致。M 为Modified,表明该cache line中的数据是Unique且Dirty的。

4.1, Modified => Owned, Invalid => Shared

接下来,让core 1,core2,core3对该地址进行读取操作,core0的状态将会从VDM 转为 VDO,其他三个core的cache line将由Invalid 转为 VS, 其中O表示Owned, S表示Shared,O状态与S状态为对应关系。此外,从下图中,也可知,core1,core2,core3读取到的数据是core0 cache中的备份,而不是真正内存中的值。

4.2 Modified => Invalid , Invalid => Modified

如果让core1写入一个新数据,core0中的数据没有被写回DDR中,发生了data corruption,core0中之前保存的数据消失了,cache line的状态变为invalid。而core1的状态将由Invalid 变成Modified,同时也是dirty的。

5,Owned => Invalid, Shared => Invalid, Shared => Modified

接4.1的步骤, 如果core1 试图对该地址写入一个新值,core0的状态将由Owned 变为 Invalid,core2和core3中该cache line的状态将会由Shared 变为 Invalid,而core1的状态将由Shared 变为 Modified(VDM)。此外,由于使用的是write back策略,所以当前的写入操作仅写入到了cache中,主存中的内容仍未改变。

在本示例中,出现了两个core先后对同一个内存地址进行读写操作, core0写入的值(蓝色)由于没有被写回到主存中,之后core1又对该地址写入一个新值(绿色),就把core0写入的值给覆盖了。

6,Clean 和Invalidate操作对MOESI状态的影响

6.1 对 Owned状态进行clean & Invalidate

如下图所示,core0的相关cache line之前处于 VDO状态,对其进行clean&invalidate操作后,core0的状态变为Invalid,其他三个core的状态依旧为 VS,并且core0 cache中的数据已写回到主存中。

6.1 对 Shared状态进行clean & Invalidate

如下图所示,core1的相关cache line之前处于 VS状态,对其进行clean&invalidate操作后,core1的状态变为Invalid,其他l两个core的状态依旧为 VS,并且core1 cache中的数据已写回到主存中。但是core0的相关cache line依旧处于 VDO状态。此时主存中的data和cache 中的data已同步,但是core0的cache line仍为dirty 状态,这是由于Clean & invalidate操作是软件主动进行的,干扰了硬件层上数据同步的正常操作流程导致的。

三, 练习题

以下是Berkeley大学的一道练习题,供大家参考:https://inst.eecs.berkeley.edu/~cs61c/su13/disc/Disc10Sol.pdf

With the MOESI concurrency protocol implemented, accesses to cache accesses appear serializiable. This means that the result of the parallel cache accesses appear the same as if there were done in serial from one processor in some ordering.

Quiz 1: Consider the following access pattern on a two‐processor system with a direct‐mapped, write‐back cache with one cache block and a two cache block memory. Assume the MOESI protocol is used, with write‐back caches, write‐allocate, and invalidation of other caches on write (instead of updating the value in the other caches).

四,注意事项

硬件层上数据一致性的维护 需要先使能CPU扩展控制寄存器(CPU Extended Control Register) 的SMPEN bit,该寄存器提供了一些额外的处理器配置和控制选项。其中SMPEN位:

CPUECTLR[6]:SMPEN,在当前cluster中,使能硬件对在多个core中的数据一致性管理,为0时,将会禁止在多个core中的数据一致性维护功能,这也是 reset value。为1时,使能数据一致性功能。所以即便是在只有一个core的系统中,也建议在enable 缓存前先将SMPEN置为1,否则缓存里的数据将不会与其他core同步,将可能发生data corruption。

参考文章:

DDI0500J_cortex_a53_trm.pdf 文章来源:https://www.toymoban.com/news/detail-715826.html

https://inst.eecs.berkeley.edu/~cs61c/su13/disc/Disc10Sol.pdf文章来源地址https://www.toymoban.com/news/detail-715826.html

到了这里,关于ARMv8-缓存一致性(cache coherency)解决方案:MOESI protocol的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!