重要提示!此教程只用于学习用途!

目录

安装包提供

Quartus II 15.0(Cyclone V器件库)与ModelSim 10.5 的安装步骤

2023年9月12日补档,Quartus与ModelSim的关联。

文章来源地址https://www.toymoban.com/news/detail-716623.html

安装包提供

教程使用的安装包,均为网络开源资源,侵权立删。百度网盘链接:百度网盘 请输入提取码提取码:hq4n

Quartus II 15.0(Cyclone V器件库)与ModelSim 10.5 的安装步骤

1.网盘下载这两个压缩包,下载路径别放在C盘,避免容量不足报错

2.打开windows安全中心的病毒和危险防护设置

3.管理设置

4.关闭这两项

5.解压第一步的两个压缩包,并将解压后的内容放在同一个文件夹内,文件夹路径不能有中文和非法字符.

6.右键管理员运行QuartusSetup-15.0.0.145-windows

7.点击next

8.选择同意,next

9.选择安装路径,路径不能有中文和非法字符,不要选C盘,记住此路径,next

10.进入该界面,检查选项是否勾选上了Cyclone V(第五步完成的前提,即Cyclone V的芯片包与Quartus安装包同意路径,此界面才会出现Cyclone V的选项),若没勾选就自己勾选上,next

11.next

12.等待,安装进度条完成后,next

13.安装完成后的界面如下图所示,勾选上这三个然后finish。

14.弹出此驱动安装界面,点击下一页

15.弹出这个,选择安装

16.状态为可以使用,然后点击完成。

17.弹出这两个弹窗,直接叉掉

18.打开文件夹:Quartus_II_15.0XX

19.右键管理员运行:Quartus_II_15.0XXX

20.在软件中,点击查找

21.在第9步的路径中找到quartus文件夹,双击进入文件夹

22.双击进入bin64文件夹

23.找到文件,选择然后打开

24.下一步,弹窗点击确定

25.点击完成,成功补丁点击确定

26. 双击打开桌面Quartus II 15.0 (64-bit)应用,弹窗选择If you have license…,然后OK

27.弹出此界面

28.然后回到第19步文件夹内,双击打开lincense,用记事本打开

29.在此界面找到HOSTID= "XXXXXXX "

30.复制此界面的ID的第一个逗号前的ID号

31.将第29步HOSTID= "XXXXXXX "双引号内的内容更改为第30步复制的ID,更改完毕后保存

32. 然后另存为到第9步的路径中找到quartus文件夹中的licenses文件夹内

33.回到此界面点击这三个小点

34.找回第32步另存为的文件,选择并打开

35.然后点击OK

36.弹出软件界面即为Quartus安装完成

37.接下来安装Modelsim 回到解压文件的文件夹中,右键管理员运行ModelSimSetup-16.1.0.196-windows

38.进入安装程序界面,next

39.选择第一个,next

40.同意,next

41.选择路径,与第9步的路径一致!next

42.next

43.等待安装进度

44.完成后,不要勾选,finish

45. Quartus II 15.0(Cyclone V器件库)与ModelSim 16.1全部安装完成。

文章来源:https://www.toymoban.com/news/detail-716623.html

2023年9月12日补档,Quartus与ModelSim的关联。

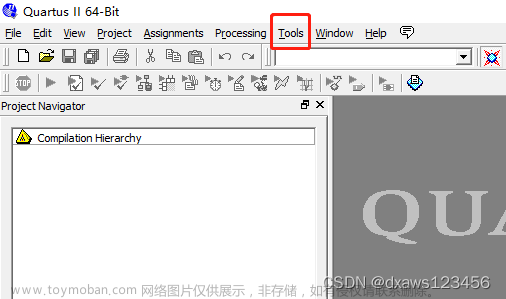

1.打开Quartus,左上角工具栏选择:Tools->Options...

2.General->EDA Tool Options->ModelSim-Altera(最下面那行),点开右侧三个小点

3.找到Quartus的安装路径,双击打开modelsim_ase文件夹

4.下滑找到win32aloem该文件并选中,然后单击选择文件夹

5.第2步界面ModelSim-Altera(最下面那行)出现第4步选择的路径后,点击OK

6.新建工程,File->New Project Wizard...

7.next后进入到创建工程路径和工程名,选择一个工程存放路径并为工程命名(不能有中文和非法字符),完成后next

8.Project Type->Empty project->next

9.Add Files 先跳过,直接next。进入到Family&Device Settings界面,博主选择的是5CEBA4F23C7,可以自己的实际使用情况选择不同的芯片支持包,选择之后next。

可以不选直接next

10.进入到EDA Tool Settings界面,在Simulation这一行,Tool Name 选择ModelSim-Altera,Format选择Verilog HDL(看实际使用情况选择),选择完毕后next

11.最后到了Summary,可以查看新建工程的详细内容,无误就点击Finish,完成新建工程

12.然后左上角点击白纸New

13.选择Design Files->Verilog HDL File->OK

14.输入一个测试内容

module exp01(a,b,c);

input [1:0] a,b;

output [2:0] c;

assign c = a + b;

endmodule 15.点击保存Save(白纸New的右侧),或者快捷键Ctrl+S进行保存

16.弹出此窗口,直接点击保存

17.左上角Assignments->Settings...

18.点击EDA Tool Settings->Simulation,右侧窗口中,Tool name选择ModelSim-Altera,中间EDA Netlist Writer settings->Format for output netlist选择Verilog HDL,下方NativeLink settings选择Compile test bench

19.点击Compile test bench这一行最右侧的Test Benches...,点击New...

20.弹出此窗口,点击File name 这一行右侧的三个点

21.直接选择exp01_tb.v这个文件,Open

22.然后将exp01_tb填写在Test bench name 这一行,Top level...这一行会自动填充,然后File name 这一行最右侧的Add,点击Add

23.下方表格中出现exp01_tb.v后,然后一直点击OK

24.左上角工具栏中,Processing->Start,点击Start Analysis & Synthesis。

25.等待右下角进度加载完成,且下方信息栏中出现0 errors,0 warnings

26.左上角工具栏中,Tools->Run Simulation Tool,点击RTL Simulation

27.弹出ModelSim界面,则Quartus与ModelSim关联成功。

感谢观看。

到了这里,关于FPGA必备软件保姆级教程:Quartus II 15.0(Cyclone V器件库)与ModelSim 10.5 的安装教程的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!