一、问题描述

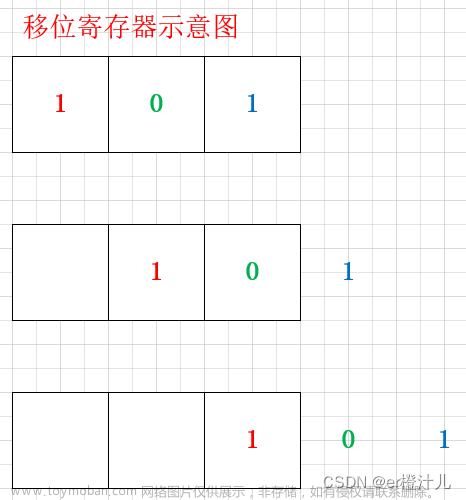

这项练习是module_shift移位寄存器的延伸。模块端口不是只有单个引脚,我们现在有以向量作为端口的模块,您将在其上附加线向量而不是普通线网数据。与 Verilog 中的其他位置一样,端口的向量长度不必与连接到它的导线匹配,但这会导致向量的零填充或截断。本练习不使用向量长度不匹配的连接。

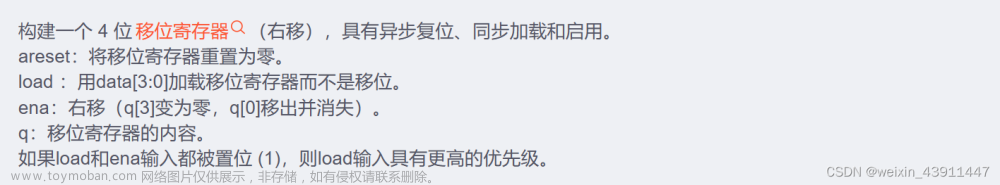

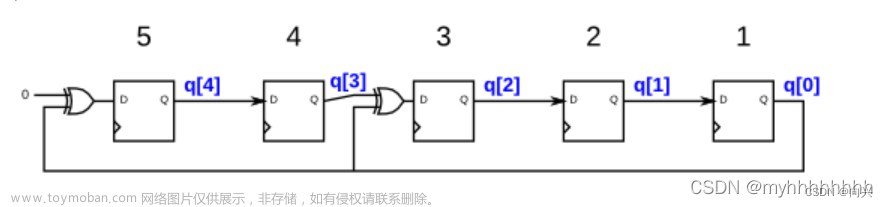

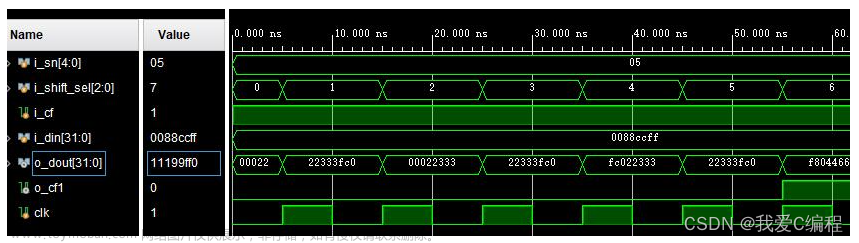

您将获得一个具有两个输入和一个输出的模块 my_dff8 (实现一组 8 D 触发器)。实例化其中三个,然后将它们链接在一起,形成长度为 3 的 8 位宽移位寄存器。此外,创建一个 4 对 1 多路复用器(未提供),该多路复用器根据以下条件 sel[1:0] 选择要输出的内容:输入 d 处的值、第一个 d 触发器输出、第二个或第三个 D 触发器的输出。(实质上,选择延迟输入的周期数, sel 从零到三个时钟周期。

提供给您的模块是: module my_dff8 ( input clk, input [7:0] d, output [7:0] q );文章来源:https://www.toymoban.com/news/detail-716672.html

未提供多路复用器。一种可能的编写方法是在 always 块内使用 case 语句。文章来源地址https://www.toymoban.com/news/detail-716672.html

到了这里,关于hdlbits系列verilog解答(8位宽移位寄存器)-24的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!