ERROR: [Labtools 27-3165] End of startup status: LOW

ERROR: [Common 17-39] 'program_hw_devices' failed due to earlier errors.

在烧录bit流文件时,出现烧录不进去,报以上的错误。问题情况不分先后顺序,自行测试

第一种情况:检查vivado型号是否正确

第二种情况:硬件问题或者电路问题

- 首先排查焊接问题。

- 降低JTAG下载速率。

- 重启Vivado/ISE。

- 下载器不适配,试试相同属性板子是否能够与下载器适配。

- 还有可能芯片部分损毁,换一块片子试试。

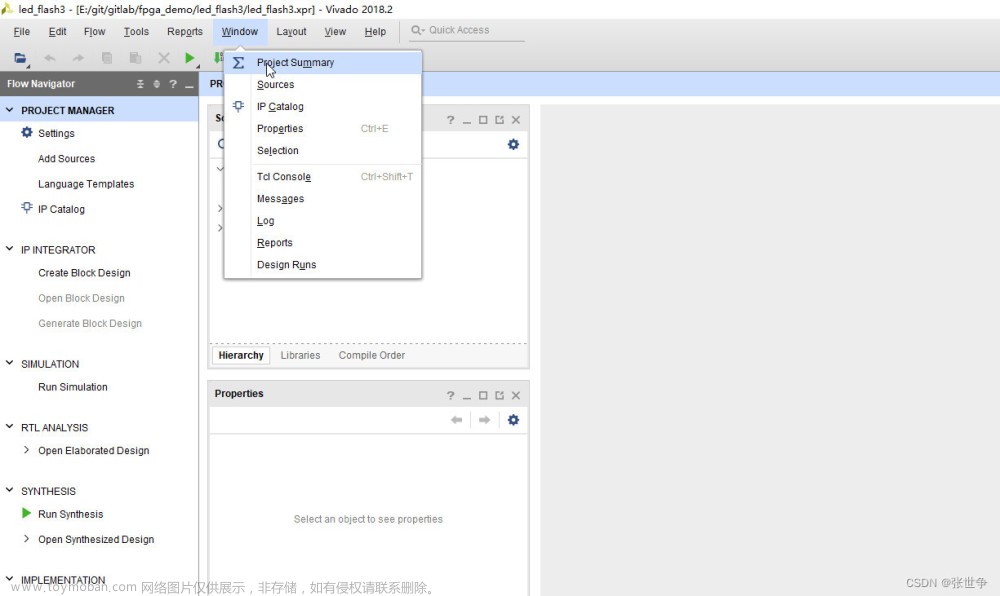

第三种情况: 引脚电平问题

文章来源:https://www.toymoban.com/news/detail-717098.html

文章来源:https://www.toymoban.com/news/detail-717098.html

与PCB工程师确定引脚上拉还是下拉,这是电路的设置,在vivado中尽量不要去修改,还是让电路更改为好。,如果电路实在无法更改再更改这里的设置。以我的建议还是重新更改电路为好,要么重新设计电路。文章来源地址https://www.toymoban.com/news/detail-717098.html

到了这里,关于vivado FPGA烧录报错的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![VIVADO报错:[opt31-67]之MIG ip核综合失败](https://imgs.yssmx.com/Uploads/2024/02/535711-1.png)