Verilog数字系统设计——4 选1 多路选择器

题目

- 试分别使用assign、门级原语和always 语句设计4 选1 多路选择器,并写出测试代码进行测试。要求编制测试模块对实现的逻辑功能进行完整的测试;

- 实验提交Verilog设计文件(.v文件)和仿真波形截图,文件打包,压缩包以自己的学号+姓名命名;

仿真截图

代码

下面展示一些 内联代码片。文章来源:https://www.toymoban.com/news/detail-717110.html

// An highlighted block

always语句:

module four_to_one_1(out,a,b,c,d,s1,s0);

output out;

reg out;

input a,b,c,d;

input s1,s0;

always @(a or b or c or d or s1 or s0)

begin

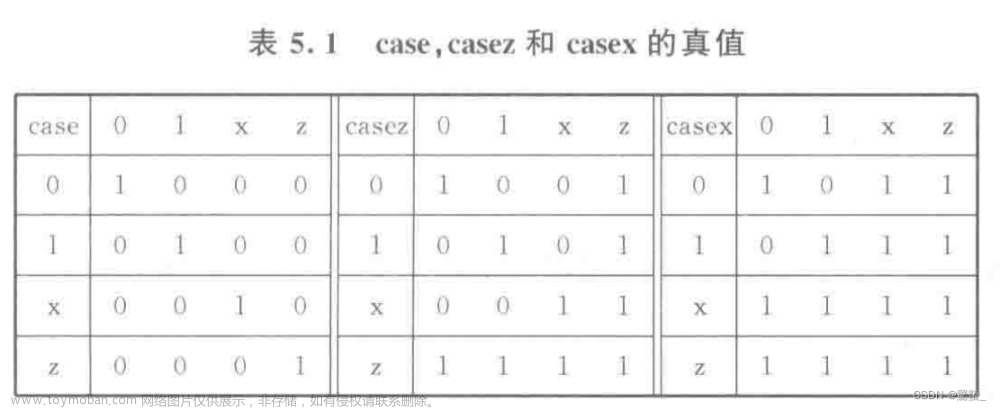

case({s1,s0})

2'b00: out=a;

2'b01: out=b;

2'b10: out=c;

2'b11: out=d;

default: out=0;

endcase

end

Endmodule

Assign语句

module four_to_one_2(out,a,b,c,d,s1,s0);

output out;

input a,b,c,d;

input s1,s0;

assign out=s1?(s0?d:c):(s0?b:a);

endmodule

门级:

module four_to_one_3(out,a,b,c,d,s1,s0);

output out;

input a,b,c,d;

input s1,s0;

wire out1,out2,out3,out4;

not u1(ns1,s1);

not u2(ns0,s0);

and u3(out1,ns1,ns0,a);

and u4(out2,ns1,s0,b);

and u5(out3,s1,ns0,c);

and u6(out4,s1,s0,d);

or u7(out,out1,out2,out3,out4);

endmodule

module four_to_one_test;

wire outw1;

wire outw2;

wire outw3;

reg ain,bin,cin,din;

reg s0in,s1in;

four_to_one_1 four_to_one_1(.out(outw1),.a(ain),.b(bin),.c(cin),.d(din),.s1(s1in),.s0(s0in));

four_to_one_2 four_to_one_2(.out(outw2),.a(ain),.b(bin),.c(cin),.d(din),.s1(s1in),.s0(s0in));

four_to_one_3 four_to_one_3(.out(outw3),.a(ain),.b(bin),.c(cin),.d(din),.s1(s1in),.s0(s0in));

initial

begin

ain=1'b0;

bin=1'b0;

cin=1'b0;

din=1'b0;

s1in=1'b0;

s0in=1'b0;

end

always #10 {s1in,s0in}={s1in,s0in}+1'b1;

always #10 {ain,bin,cin,din}={ain,bin,cin,din}+1'b1;

endmodule

运行截图

文章来源地址https://www.toymoban.com/news/detail-717110.html

文章来源地址https://www.toymoban.com/news/detail-717110.html

到了这里,关于Verilog数字系统设计——4 选1 多路选择器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!