目录

前言

一、什么是模块

二、模块的内容

1.I/O声明的格式

2.内部信号的声明

3.功能定义

三、模块的调用(例化)

要点注意

前言

本次的学习内容是verilog的基本设计单元:模块(module)

一、什么是模块

模块(module)是verilog设计基本单元。一共由两部分组成:一部分是描述接口,另一部分描述逻辑功能。下面将举个例子说明模块的基本构成:

module mux2_1(a,b,sel,mux_out);

input a,b; //****************//

input sel; //****端口描述****//

output mux_out; //***************//

assign mux_out = (sel==1)?a:b; //**逻辑功能描述**//

endmodule例1.1

这段代码实现的功能是二选一多路选择器,其中

●a,b,sel作为输入端口,mux_out作为输出端口,第2-4行的代码就完成了端口的描述。

●通过三目运算符的操作,第5行代码完成逻辑功能的描述。

●mux2_1为用户自定义模块名,整个模块以module开头endmodule结尾

二、模块的内容

1.I/O声明的格式

module 模块名(端口名1,...,端口名m+n+k);

input [信号位宽-1:0] 端口名1;

.

. //**i个输入**//

.

input [信号位宽-1:0] 端口名m;

output [信号位宽-1:0] 端口名m+1;

.

. //**n个输出**//

.

output [信号位宽-1:0] 端口名m+n;

inout [信号位宽-1:0] 端口名m+n+1;

.

. //**k个双向口**//

.

inout [信号位宽-1:0] 端口名m+n+k;

也可以定义成如下格式:

module 模块名(

input [信号位宽-1:0] 端口名1,

.

. //**i个输入**//

.

input [信号位宽-1:0] 端口名m,

output [信号位宽-1:0] 端口名1,

.

. //**n个输出**//

.

output [信号位宽-1:0] 端口名n,

inout [信号位宽-1:0] 端口名,

.

. //**k个双向口**//

.

inout [信号位宽-1:0] 端口名k

);

注意两种定义的区别:

第一种是在括号结束后进行定义,因此每个语句用分号 ; 结束。

第二种是在括号内部进行的定义,因此每个语句用逗号 , 连接。

2.内部信号的声明

当某些信号不是作为输入或输出信号,而是作为中间信号被我们所用到,那么就需要声明。

格式如下:

wire [信号位宽-1:0] W变量1;

reg [信号位宽-1:0] R变量1;

.

.

.

这里的wire与reg是数据类型,下一节展开讲。

3.功能定义

模块中最重要的部分就是逻辑功能定义部分,由以下三种方法来产生逻辑:

(1)用assign语句,如例1.1中:assign mux_out = (sel==1)?a:b;

assign只适用于组合逻辑,且描述只需assign后面接一个方程式即可。

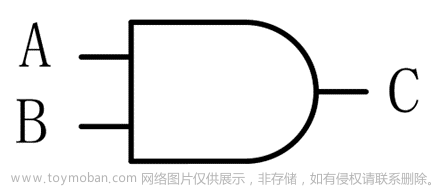

(2)用实例元件,如:and U0(out, a, b);

该方法就是调用库原件,键入元件名和相应的引脚即可。其中and就是元件名与门,U1是用户定义模块名,a,b为输入,out为输出。

注:要求模块名必须是唯一的,目的是区分调用的多个相同元件

(3)用always块,如:

always@(posedge clk or posedge rst)

begin

if(rst)

out <= 0;

else

out <= out + 1;

endalways块既可描述组合逻辑,又可描述时序逻辑。

三、模块的调用(例化)

模块调用语句格式如下:

module_name instance_name(port_associations);

其中module_name是被调用模块的模块名,instance_name是用户定义的引用名,port_associations是现模块与原模块之间信号端口的关联方式。而关联方式的格式有如下两种:

(1)在引用时用“.”符号表明是原模块定义的端口名,()里表示的是现模块的端口,如:

mux2_1 M0(

.a(A),

.b(B),

.sel(Sel),

.out(Out),

);

相当于把这2选1多路选择器调用到现在这个模块,现在这个模块有A,B,Sel,Out这些信号端口,将A与原模块中的a对应,B与原模块中的b对应,Sel与原模块中的sel对应,Out与原模块中的out对应。意义就是把现模块的A,B,Sel分接入到二选一多路选择器的输入端,那么Out输出的就是Sel选择A,B的结果。

(2)引用时,严格按照原模块端口顺序连接,无需标注原模块端口名称,如:

mux2_1 M0(A,B,Sel,Out);

表3.1 端口关联关系

模块调用注意事项:

(1)两种关联格式不能混用,即不可这样写:mux2_1 M0(A,.b(B),Sel,Out);

(2)不能以循环方式嵌套模块,即不能在always语句里调用模块。

要点注意

1. 如果assign、例化元件、always三者在同一模块中,这三种逻辑功能描述是同时进行的。也就是说,无论这三个描述代码先后顺序如何,他们都是并行的。

2.但是对于always块来说,逻辑是按照指定顺序执行的,因此always也称为过程块。

总的来说,verilog中的所有过程块、连续赋值语句(assign)、实例引用都是并行的.

参考资料:文章来源:https://www.toymoban.com/news/detail-717262.html

文章来源地址https://www.toymoban.com/news/detail-717262.html

文章来源地址https://www.toymoban.com/news/detail-717262.html

到了这里,关于1、verilog语法——模块的结构的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!