本作品参与极术社区组织的有奖征集|秀出你的集创赛作品风采,免费电子产品等你拿~活动。

团队介绍

参赛单位:合肥工业大学

队伍名称:芯创之家

指导老师:邓红辉、尹勇生

参赛杯赛:Arm杯

参赛人员:王亮 李嘉燊 金京

获奖情况:全国总决赛三等奖

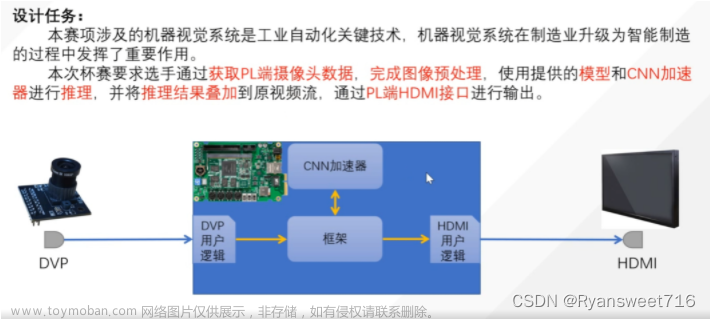

1.项目简介

人脸检测系统在诸多领域都有实际作用,比如自动进行出入登记:人员或车辆出入小区时可自动抓拍扫描记录,省去人工记录,省时省力;安防应用:可利用此识别技术对小区常住人口和流动人口进行分类识别,对可疑人员行动轨迹提前预警,为小区安防工作带来极大便利。并且本设计可以不断扩展,用于识别车辆、设备等,更换算法后还可以实现人脸识别,应用于管理或者刑侦破案中,可以通过训练以识别一些难以观察到的微小疾病,用于医学观测。

本SoC是基于ARM官方提供的Cortex-M3软核和Xilinx Artix-7系列开发板实现,使用AMBA2和AMBA3总线协议以及ARM提供的CMSDK工具设计SoC。外设搭配一个摄像头用于数据的采集,一个液晶显示屏用于显示处理结果,同时绑定数码管显示人脸数量等信息。基于Viola-Jones算法完成人脸检测的功能,实现了Viola-Jones算法完成人脸检测的功能。

2.系统运行流程介绍

a. 在线上使用PyTorch等前端框架对该算法进行训练,得到权重等参数提前存储在FPGA例化的RAM中,用C语言完成算法的实现,生成相应的指令存储在例化好的RAM中。

b. 摄像头采集图像数据,传递给Cortex-M3处理器。

c. 处理器接收图片后,开始读取指令和参数,调用FPGA的计算资源进行计算

d. 算法完成后将处理好的图像数据通过HDMI传递到显示屏,并将一些信息传递给绑定的数码管,完成输出结果的显示。

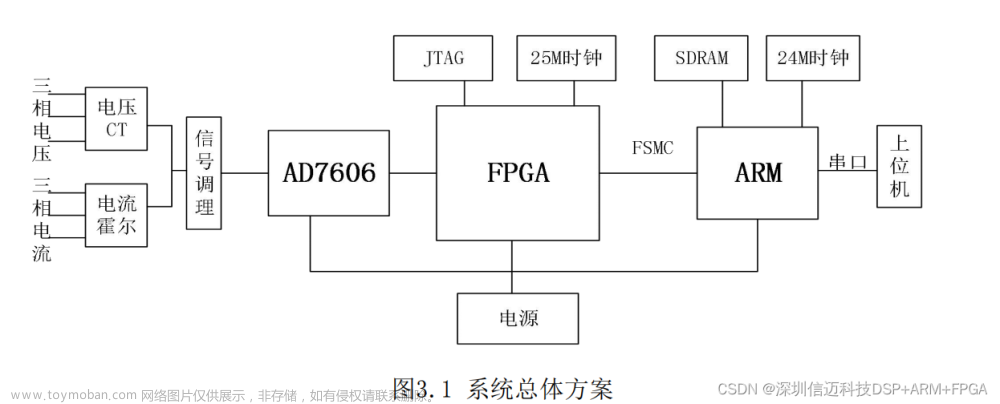

3.系统架构

3.1架构简介

本系统的架构如下图3.1所示。整个框架搭载在一块FPGA开发板上。可简单地分为软件和硬件两个部分,Cortex-M3和上面的RAM是软件部分,RAM中存储指令,ARM处理器通过轻量级的AHB总线协议和它通信,通过指令总线取指,通过数据总线进行数据访问。可以使用Keil在线调试SoC,通过J-link连接开发板与PC机,将C语言代码编译成的汇编代码烧录至指令RAM中即可。

图3 1整体系统架构图

3.2软硬件功能划分

软件部分主要包括Cortex-M3和上面的RAM是软件部分。硬件部分主要用于数据采集和计算,我们将高速外设(显示器、摄像头等)和低速外设(LED、UART等)分别挂载到不同的总线上,这样可以避免资源的浪费。

4.外设挂载

4.1 液晶显示屏

图4.1 1 显示屏模块框架

上图是显示屏模块,摄像头采集到的数据会存储在DDR中供处理器和显示屏读取,处理器计算结束后会将画框后的图片通过AHB-AXI转换传输到DDR,DDR再经过HDMI传递到显示屏上。HDMI驱动里使用了两个FIFO来避免读写时的数据冲突。

4.2 摄像头

图4.2 1 摄像头模块框架

上图3所示是摄像头模块的框架,摄像头用于采集数据,并将采集数据传送给DDR,与显示屏类似,我们也使用了FIFO避免数据冲突。由于我们使用的摄像头采集的图像中,每个像素点的位数为16bits,但总线协议每个时钟周期只能传送8bits,因此需要首先经过一个位宽转换器,打一拍完成像素完整传递后再传递给FIFO模块。其余模块再通过相应的总线发出请求从DDR中读写数据。

4.3 数码管和LED灯

开发板上有一个四位数码管和四颗LED灯,我们使用LED来显示程序是否正常运行,数码管用来显示人脸的数量,四颗LED同时也会作为4位二进制数来表示人脸数量,最多表示15个,这些功能都是软件驱动的。

4.4 UART串口

UART串口可将识别速度等信息传送至上位机,用于监测SoC运行情况以及实时人脸检测的速度。

5.加速器设计

5.1 片上存储优化

在不使用 DMA 的情况下,内核通过 DCode 经过总线矩阵协调,使用 AHB 把外设采集的数据读取到内核,然后内核 DCode 再通过总线矩阵协调,把数据存放到内存 SRAM 中。DMA 正好可以取代这样的工作。由 DMA 控制器的 DMA 总线与总线矩阵协调,使用AHB 把外设的数据经由 DMA 通道存放到内存 SRAM。如果使用DMA,它是不经过内核的直接传到了SRAM,因此加快处理速度,MCU也可以处理其他事情 ,起到了给芯片减负的效果。因此可以将DDR换成DMA。

AC7050 核心板上配有两个 Micron(美光) 的 4Gbit( 512MB) 的DDR3 芯片(共计 8Gbit),型号为 MT41J256M16HA-125(兼MT41K256M16HA-125)。 DDR 的总线宽度共为 32bit。 DDR3 SDRAM 的最高运行时钟速度可达 333.3MHz(数据速率667Mbps)。该 DDR3 存储系统直接连接到FPGA 的BANK34和 BANK35的存储器接口上。因此可以将数据存储到DDR3中之后在由加速器读取里面的数据从而提高数据处理速度。

图5.1 加速器整体框架

当摄像头完成前两帧数据采集后开启目标检测单元,加速器模块与DDR交换数据并计算相关参数,检测完成后将目标进行框选,开始运行目标跟踪算法。

图5.1 DDR3 DRAM原理示意图 1

5.2 多线程移窗

在所用到的算法中采用决策时级联检测器是把摄像头采到的数据进行取。传统的采集方案是逐行检测这样会降低检测,因此需要前一步完成采集 才能进入下一步采集是一种串行运行的方式。因此提出并行采集的方案,采用多个加速器组成了一个多线程的并行加速器,因此就可以处理多个窗的数据检测,从而提高了人脸检测的速度。

6.模块及系统仿真

7.系统整体测试结果

在硬件平台上实现系统,并正确编译、下载软件程序, 现场编程调试,通过按键改变LED等的闪烁方式或频率证实系统运行情况。

·功能展示二

通过led来显示摄像头识别到的人脸数量仿真结果如下图所示。

8.参赛体会

本系统使用2001年CVPR提出的经典的人脸检测算法Viola-Jones,采用积分图像(integral image)技术,加速对Haar-like输入特征的计算,采用 AdaBoost 算法进行特征选择,选择出几个关键的视觉特征,采用检测级联技术提高准确率,允许图像的背景区域被很快丢弃,从而将更多的计算放在可能是目标的区域上,减少了计算开销算法。在算法的实现过程中,文献是非常好的工具,在文献中汇集了若干科研工作者的智慧,也在不断的实践中,修复了若干问题,在稳定性和性能方面都较好的实现。因此,通过对这些文献的认真研究,对有统一的、经过良好设计、实现、测试的基础模块适当引用,可以提高开发效率,集中注意力攻克更核心的部分。

在开发的过程中,要学习以及熟练使用各种开发工具来简化开发,如CMSDK、Matlab、system generator等。在整个系统的开发过程中,开发工具的使用至关重要,例如开发过程中需要使用CMSDK快速搭建基于CortexM3的专用SoC。对于这些软件的使用,可以大大节省时间,并且可以研发出更高效的系统。

在SoC的搭建过程中,对整体框架的把握至关重要。本次设计中,框架可分为软件和硬件两个部分,每部分的组成成为设计的重要部分,连接和通信均建立于框架的基础上,因此在设计中要结合开发板与应用需要,对各个部分进行设计划分,实现系统的统一高效协作。

在这次比赛中,很荣幸可以与全国各地200余所高校参赛队伍共同努力。非常感谢赛事组委会的老师和工作人员在本次大赛中的辛苦付出!文章来源:https://www.toymoban.com/news/detail-717848.html

作品内容来源于芯创之家,转载请标明出处。欢迎大家参加极术社区组织的有奖征集|秀出你的集创赛作品风采,免费电子产品等你拿~活动,10月1日截止~文章来源地址https://www.toymoban.com/news/detail-717848.html

到了这里,关于【2021集创赛】Arm杯三等奖:基于FPGA的人脸检测SoC设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!