萌新的FPGA学习之Vivado下的仿真入门-2

我们上一章大概了解了 我们所需要进行各项操作的基本框架 对于内部实现其实一知半解

我们先从基本的出发 但从FPGA 了解一下 vivado下的仿真入门 正好帮我把自己的riscV 波形拉一下

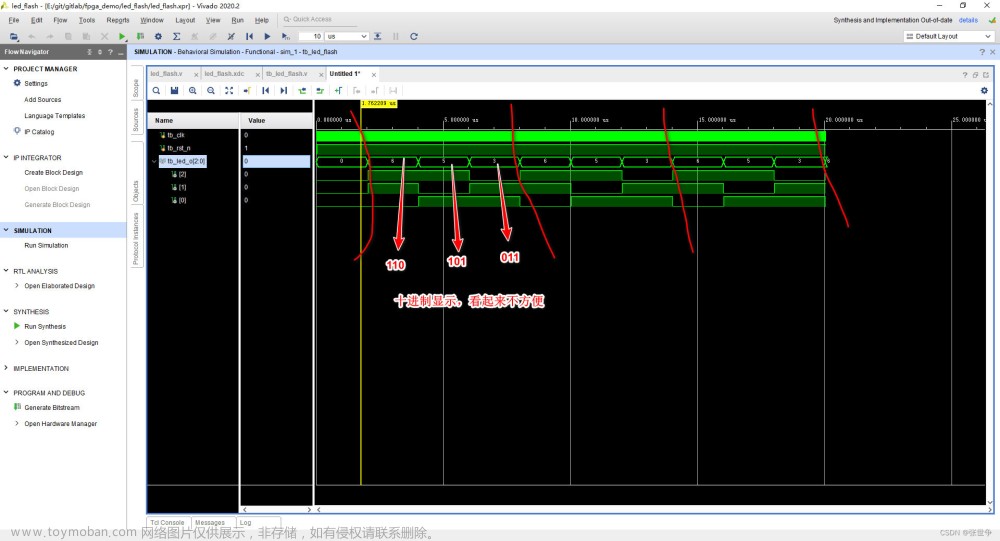

行为级仿真

step1: 进入仿真界面:SIMULATION->单击 Run Simulation->单击 Run Behavioral Simulation。

Step2:设置仿真时间,仿真时间为 1000ms。计算机 CPU 会模拟 FPGA 的运行,1000ms 运行来说通常需要几分钟时间。具体时间和 CPU 的配置有很大关系。

为了观察波形的便利,我们可以点击窗口选择float

当我们需要添加观察指定波形时,我们可以选择想要实现的信号单击add to wave window

综合 Synthesis

综合并查看报告

综合完成之后可以点击查看报告看资源的利用情况

我们可以通过报告查看资源的整体占用率

综合时序仿真

接下来我们可以执行Implementation

执行并查看报告

执行运行完毕后再次点击 文章来源:https://www.toymoban.com/news/detail-718023.html

文章来源:https://www.toymoban.com/news/detail-718023.html

查看执行完毕的报告 并且可以点开Table 看到 具体使用资料的情况 文章来源地址https://www.toymoban.com/news/detail-718023.html

文章来源地址https://www.toymoban.com/news/detail-718023.html

到了这里,关于【【萌新的FPGA学习之Vivado下的仿真入门-2】】的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!