一、quartus下载流程

1.打开Quartus工程,点击“Start Compilation”按钮进行程序全编译,如下图所示。

2.程序全编译无错误,编译信息如下图所示。

3

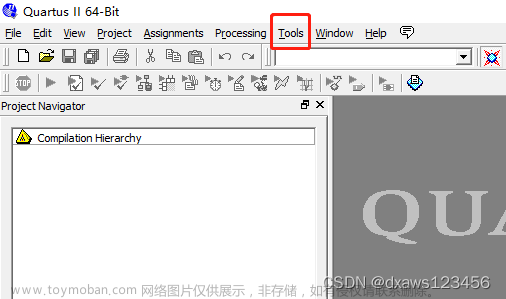

3.点击“Programmer”快捷按钮,进入程序下载页面。如下图所示。

4.选择“USB-Blaster”下载器,模式选择“JTAG”,点击“Add File”添加可执行文件“key_led.pof”并点击“Open”按钮打开,如下图所示。

5.选中“Program/Configure”复选款,点击“Start”按钮进行程序下载,如下图所示。

6.如下图所示“Progress”进程为100%时,程序下载完成。

二、quartus下载遇到的问题

如上图所示,这是博主最近遇到的问题,出现这种错误是因为下载方式选择的不对。

更改方式如下:

1.打开assignment--settings,点击右上角的device/board;

2.点击device and pin options;

3.更改下图设置匹配对应下载方式即可!

上文中参考http//jingyan.baidu.com/article/20b68a884fa174386dec627e.html。文章来源:https://www.toymoban.com/news/detail-718424.html

有关quartus其他内容的详细规划设计以及代码实现,我们下期见。文章来源地址https://www.toymoban.com/news/detail-718424.html

到了这里,关于quartus18.1--下载设置的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!