西南交大数电实验————《数字电路与计算机组成原理》

一、实验目的

- 巩固组合逻辑电路设计、仿真方法.

- 学习简单时序电路的设计与实验方法。

- 巩固 Verilog HDL 层次化文件设计。

二、实验内容

-

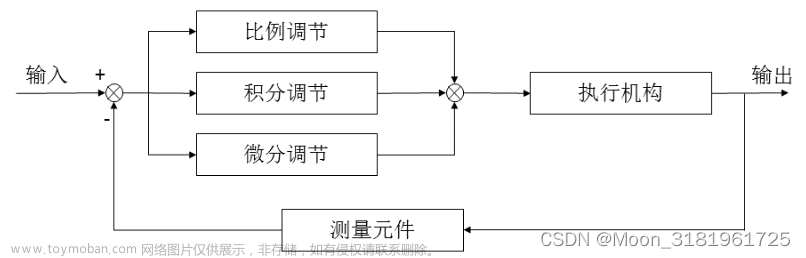

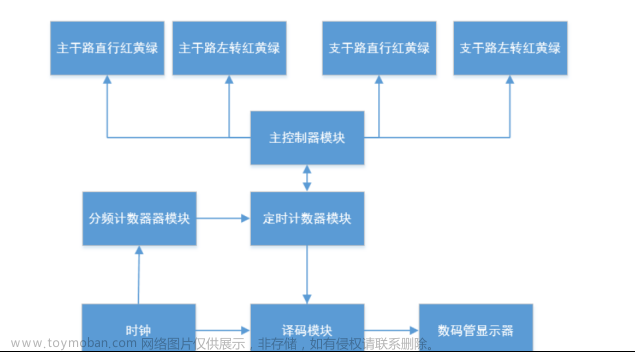

用 Verilog HDL 以层次化的设计方法(电路结构参照图 1 所示的电路框图), 设计一个 6 进制计数器及合适的译码器,将计数器输出 Q 与译码器输入 x 相连, 译码器输出codeout 锁定到实验箱的数码管段信号上(abcdefg), 实现一个彩灯控制器的设计。 数码管外圈的笔段在控制电路的驱动下, 按杨辉三角的规律依次点亮/熄灭。对整体电路进行仿真,应当能够看到使能信号 en 为低电平时电路状态保持不变, en 为高电平时计数器的输出值自动增加,相应地译码器的输出依次变化,并循环。 图 1 为顶层电路框图, 图 2 为仿真波形图。

-

引脚锁定

a) 计数器的 en 锁定到实验箱的开关 1;

b) 计数器的输出 Q 作为待观测的中间信号锁定到指示灯 LED2…LED0;

c) clk 锁定到 CLK0(PIN_88);

d) 译码器输出锁定到数码管段信号(abcdefg);

e) seg 锁定到 SEG0。 -

实验测试

a) 将实验箱的时钟 clk0 设置到 1Hz,观察数码管的显示,并用文字记录实验现象。

b) 将 clk0 设置到 PULSE,使用手动脉冲,单步调试,观察计数器输出 Q 与 codeout指示灯显示的对应关系。

c) 将 clk0 设置到 4096Hz,观察数码管的显示,记录实验现象。

d) 将 clk0 设置到 4096Hz,用导线将 clk、 Q[2:0]连接到实验箱的逻辑分析仪上(CH0~CH7)观测波形。尝试设置不同的触发字及采样率,观察逻辑分析仪显示波形的变化。画出 1 个大周期 clk 与 Q 的时序波形。

三、预习要求

- 自行查找资料, 自学 Verilog HDL 的层次化文件设计, 完成本实验“实验内容”部分的设计要求。

- 对实验电路进行功能仿真,并将仿真结果截图插入报告中。

- 列出引脚锁定分配表(信号名->主板器件名->引脚号)。

- 填写编译报告。

四、实验报告要求

- 列出通电测试结果。

- 列出实验过程出现的问题及解决措施。

- 附源程序。

五、Verilog代码、RTL视图及仿真波形

1.Verilog代码

module dzx_2_1(en,clk,Q);//模块1,产生数据Q

input en,clk;

output [2:0]Q;

reg [2:0]Q;

parameter S0=3'd0,S1=3'd1,S2=3'd2,S3=3'd3,S4=3'd4,S5=3'd5;

always@(posedge clk)

if(en)

case(Q)

S0:Q <= S1;

S1:Q <= S2;

S2:Q <= S3;

S3:Q <= S4;

S4:Q <= S5;

S5:Q <= S0;

default:Q <= S0;

endcase

endmodule

module dzx_2_2(x,seg,codeout);//模块2:数据x在数码管上的现实

input [2:0]x;

output seg;

output [6:0]codeout;

reg seg;

reg [6:0]codeout;

parameter S0=3'd0,S1=3'd1,S2=3'd2,S3=3'd3,S4=3'd4,S5=3'd5;

always@(x)

case(x)

S0:{codeout,seg}= {7'b0000001,1'b1};

S1:{codeout,seg}= {7'b0000011,1'b1};

S2:{codeout,seg}= {7'b0000111,1'b1};

S3:{codeout,seg}= {7'b0001111,1'b1};

S4:{codeout,seg}= {7'b0011111,1'b1};

S5:{codeout,seg}= {7'b0111111,1'b1};

default:{codeout,seg} = {7'b0000001,1'b1};

endcase

endmodule

module colorful_lights(en,clk,Q,seg,codeout);//顶层模块

input en,clk;

output seg;

output [2:0]Q;

output [6:0]codeout;

dzx_2_1(en,clk,Q);

dzx_2_2(Q,seg,codeout);

endmodule

2.RTL视图

3.仿真波形

文章来源:https://www.toymoban.com/news/detail-719383.html

文章来源:https://www.toymoban.com/news/detail-719383.html

欢迎在评论区留言,感谢您的关注与支持!文章来源地址https://www.toymoban.com/news/detail-719383.html

到了这里,关于数电实验4:彩灯控制器设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!