Zynq AXI_HP 接口详解

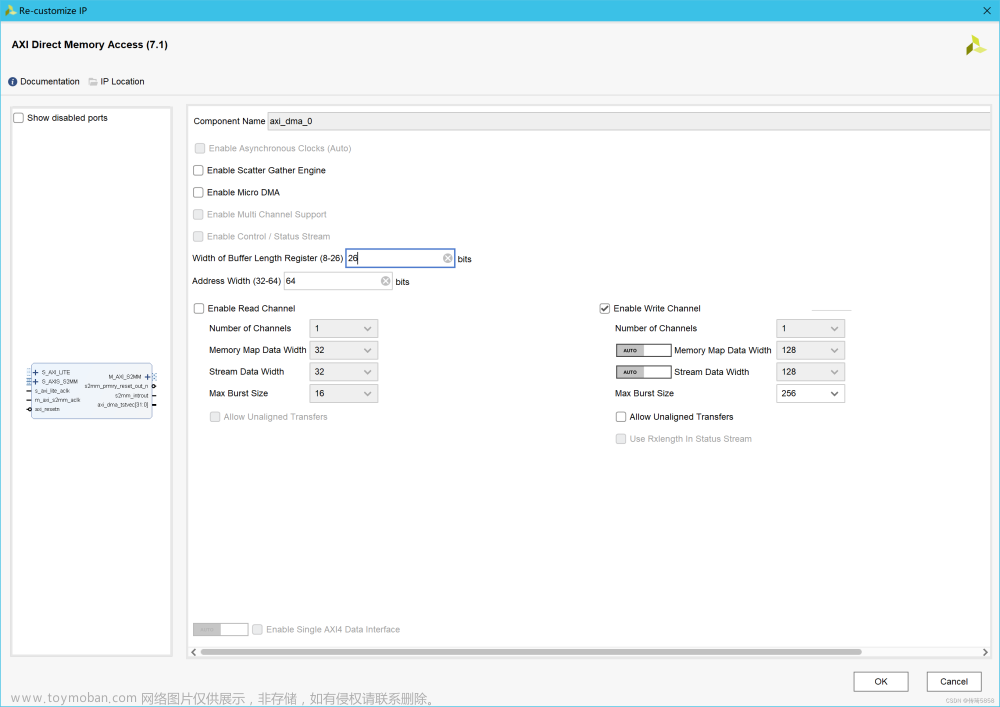

如果你是一名 FPGA 开发者,那么你一定对 Zynq 这个硬件平台不会陌生。Zynq 平台以其强大的功能和高性能而受到广泛关注。其中,AXI_HP 接口是 Zynq 平台中非常重要的一部分,它是 High Performance AXI Master 和 Slave 的缩写,具有高速数据传输和 DMA(Direct Memory Access)功能,可以实现高效的数据交换。

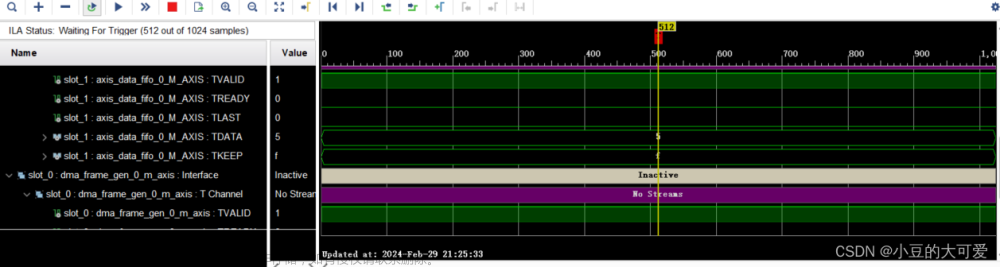

AXI_HP 是 Zynq 平台上的 AMBA(Advanced Microcontroller Bus Architecture)总线部件之一。该接口提供了两个独立的通道,Master 和 Slave。Master 可以读取外部存储器或设备中的数据,并将其传输到 FPGA 中的寄存器或存储器中;Slave 可以将 FPGA 中的数据写入到外部存储器或设备中。AXI_HP 接口还可以通过 DMA 实现内存到内存、内存到设备、设备到内存之间的数据传输。文章来源:https://www.toymoban.com/news/detail-719819.html

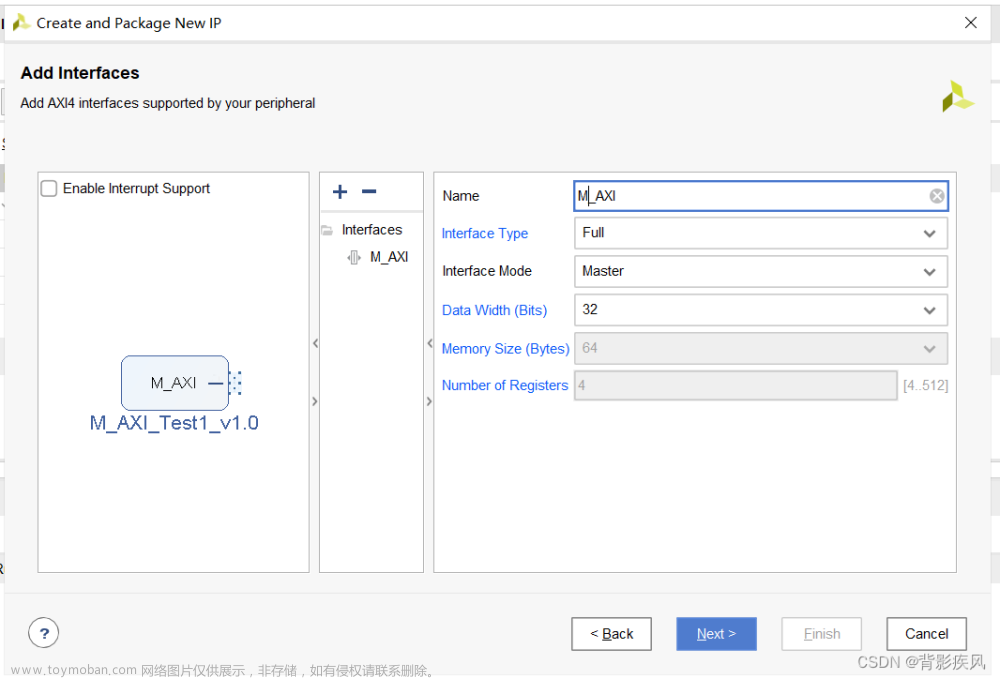

下面是一个简单的 AXI_HP 示例代码:文章来源地址https://www.toymoban.com/news/detail-719819.html

module axi_hp_test(

input wire clk,

input wire aresetn,

input wire [31:0] axi_hp_aresetn,

output wire [63:0] read_data,

input wire [63:0] write_data,

input wire read_req,

output wire read_ack,

input wire write_req,

output wire write_ack,

input wire [6:0] awaddr,

input wire [3:0] awlen,

input wire [2:0] awsize,

input wire [1:到了这里,关于Zynq AXI_HP 接口详解的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[ZYNQ]开发之MATALB与FPGA联合仿真平台设计](https://imgs.yssmx.com/Uploads/2024/02/765704-1.png)