【摘要】

通信产品一般采用分散供电方式,各单板上采用DC/DC模块将-48V电源转换为其所需的5V、3.3V、2.5V等子电源。由于输入电压高,电源电路中又存在用于滤波和防止DIP的大电容,在单板插入上电时,会对-48V电源造成冲击,瞬时大电流将造成-48V电源电压出现跌落,可能影响到其它单板的正常工作;同时,由于瞬时大电流的原因,单板插入时在接插件上会产生明显的打火现象,这会引起电磁干扰,并对接插件造成腐蚀。为了避免上述现象,-48V电源供电单板需要“缓慢”上电。

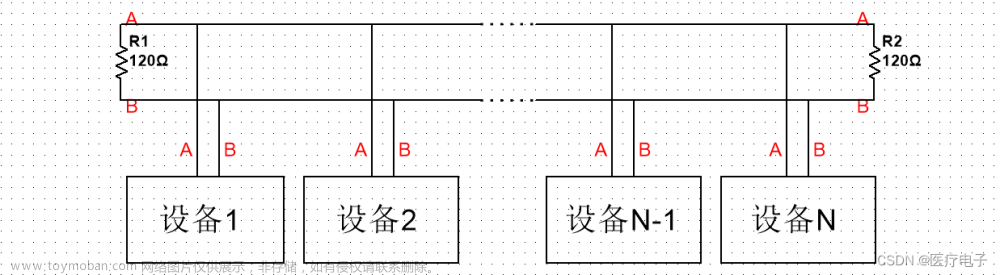

一、缓启动电路的作用

通信设备产品单板上几乎都在电源模块的输入端设计有缓启动电路,缓启动电路的功能主要有两个: 1、延迟单板电源的上电时间:我们的单板一般都要求支持热拔插,当单板插入子架时,单板插头和母板插针的接触是不稳定的,为了避免这种抖动的影响,可以在电源模块和母板电源之间加一个电路,使母板的电源延迟一段时间以后再加到电源模块。 2、减小上电的冲击电流:由于单板电源都接有滤波电容,电源上电瞬间跳变时由于电容的充电,会产生较大的冲击电流,造成母板电源电压抖动,跌落,以及强烈的电磁辐射,很容易对其他工作中的单板造成不良影响,如果能把电源的上电速度变缓一些,就能有效的减小这种影响。

二、缓启动电路的工作原理

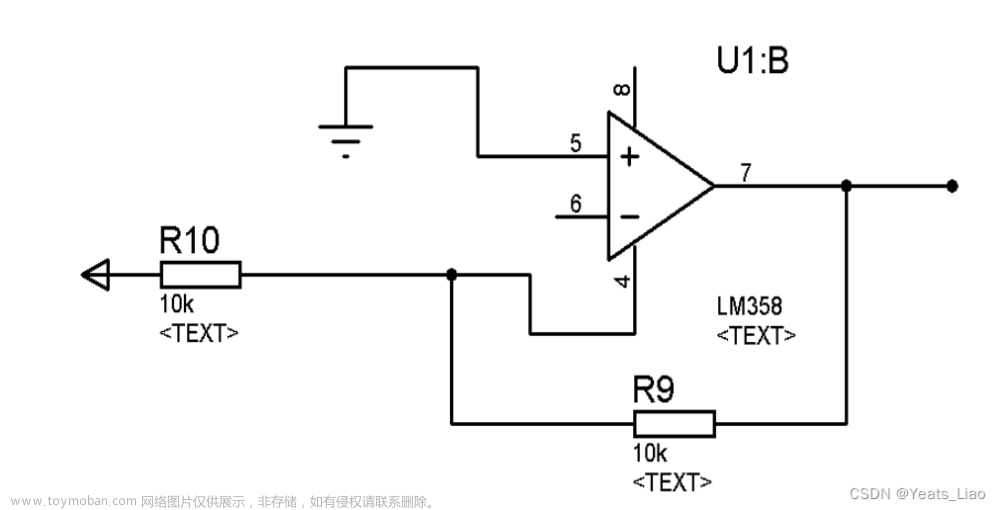

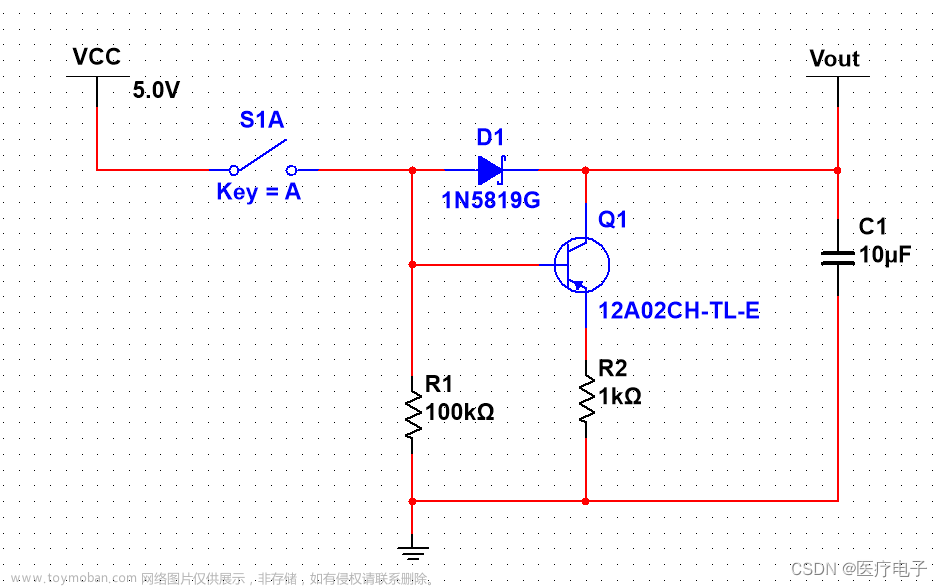

电路的原理图:

缓启动电路由R39,R49,C7和Q31组成,Q31是绝缘栅型场效应管,也是缓启动电路最关键的器件。为了理解缓启动的原理,首先我们来回顾一下MOS管的一点基础知识。下图大致描述了典型的MOS管的转移特性:

MOS管的特性表明,当Vgs小于一定电压(Vth)时,DS极之间的电阻Rds是很大的,可以认为开路,电流不能通过;当Vgs达到Vth时,MOS管开始导通,Rds随Vgs的增加迅速减小。当Vgs达到一定的程度,Rds很小,可以认为DS之间是近似短路的。Vth可以称之为开启电压(Voltage-Gate threshold),一般为2-4V。 在的缓启动电路中,电阻R39,R49和C7构成了分压式RC时间常数电路,C7并联在Q31的GS极之间,也就是Vc7=Vgs。当48V电源刚加到单板时,C7未充电,Vgs=0,MOS不导通,电源模块不供电。随后,48V通过R39,R49向C7充电,当C7的电压达到Vth时,MOS开始导通,这一阶段,完成的是延时上电的作用,延迟时间可由下式估算:

Uin(R39/(R39+R49))(1-e-T/ )=Vth其中,T为延迟时间, Uin=48V,为RC电路的时间常数,=C7(R39//R49),Vth一般取4V。将原理图中数值代入计算可知,延迟时间T约等于15.3ms。 MOS管开始导通后,Vgs继续增加(直到12V左右),Rds迅速减小,缓启动的输出电压逐渐升高直到到与输入电压基本一致。电源模块开始工作,单板正式上电。在这一过程中,输出电压并不是瞬间跳变到最高的,因此,大大减轻了冲击电流的干扰。这一过程的时间与C7的充电速度,MOS的特性,负载特性都有关系,难以具体计算,具体还需实测调整。

三、实测波形分析

下图是缓启动的输入电压上电波形

这是缓启动输入端在电源开关闭合瞬间的波形,可以看到画圆圈处的抖动,持续时间约1ms,如果是热拔插,这个抖动的幅度和持续时间都将可能更大。 下图是缓启动的C7电压上升波形

可以看到,上电15ms后,C7电源上升到约4V,与理论计算值基本一致。 下图是缓启动MOS管的D,S间电压波形。

可以看到,在开关闭合后的14ms以内,输入电压完全加在MOS的DS两端,这与理论计算值基本一致(由于MOS管的Vth并不一定是4V,有些误差是很正常的),从14ms开始,Vds以指数方式下降,过程时间约4ms。 下图是缓启动输出的电压波形。

可以看到,对比缓启动的输入电压上电波形,缓启动的输出电压不再有开关闭合时的抖动,而且上电边沿也非常明显,过程约4ms,实现了减小上电冲击的目的。 让我们再把所有的波形放在同一时间轴上来比较一下,如下:

可以看到,经过缓启动电路之后,单板实际供电电压Uout比输入电压Uin总共延时了将近20ms,不但消除了上电抖动,而且有效减小了冲击。

四、总结

1、缓启动的时间常数电路必须确保电容充电完成后其电压不能大于15V,因为一般大功率MOS管的G,S间击穿电压在20V左右,电压过高,会损坏MOS管(现在很多单板上在电容两端并联了一个稳压管就是起这个作用的),但是也不应该低于10V,因为一般大功率MOS管的D,S间电阻Rds都需要Vgs达到10V后才达到最小值(一般在0.1ohm量级)。文章来源:https://www.toymoban.com/news/detail-720019.html

2、缓启动的延迟时间不能太长,原因有二。其一,延迟太长,热拔插时,单板接口信号线已连接,而电源仍未上电,会造成接口器件闩锁损坏;其二,缓启动关键器件MOS管在从截止到导通转换的过程中瞬间功耗是非常大的,如果电容充电过于缓慢,造成边沿时间太长,MOS管将因为功耗过大而损坏。延时一般取几十毫秒。文章来源地址https://www.toymoban.com/news/detail-720019.html

到了这里,关于【电路设计】缓启动电路的工作原理的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!