系列文章目录:FPGA原理与结构(0)——目录与传送门

一、MUX概述

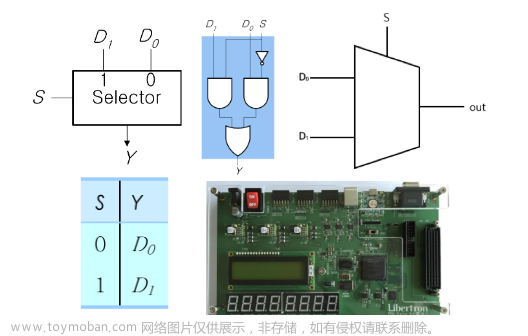

数据选择器MUX是一种非常经典的组合逻辑电路,它是一个多输入,单输出的器件,功能是可以根据选择信号,选择出需要的输入信号作为输出。

二、FPGA中的MUX

MUX在FPGA中的CLB中,我们打开device视图放大观察可以看到

图片中红色部分标注的就是MUX,可见MUX是作为一种基本元件存在于FPGA中的。但是我们同样知道,MUX作为一种组合逻辑元件,理论上完全可以通过LUT(关于LUT的部分:FPGA原理与结构——查找表LUT(Look_Up_Table))就实现其功能,为什么在FPGA中还要“多此一举”专门放入MUX元件呢?

其实在FPGA中,在实现MUX2,MUX3,MUX4时都是只采用了LUT结构。接下来我们以MUX4为例,来看一下fpga如何通过LUT来实现MUX。

首先每个6-LUT都可以被配置成一个MUX4,因此一个slice中最多可以配置4个MUX

其实MUX4_1本质上就是一个LUT6,只不过它有着特定的连线方式,它将2位地址输入,以及4位数据输入连入到LUT6的地址输入端。同样的MUX2,MUX3都可以通过LUT进行实现。

接下来我们考虑当需要选择的信号大于4时的情况,此时LUT的6个输入端口显然就不够用了。这时候会需要用到我们FPGA中的MUX资源了。我们以MUX8为例

在使用LUT的基本上还用到了MUX资源,在每个slice中有一个F7BMUX和一个F7AMUX,这两个MUX将两个lut的输出组合起来,形成一个多达13个输入(或一个8:1的MUX)的组合函数。在一个slice中最多最多可以部署两个MUX8。

但是这还不是我们一个slice所能够做到的极限,既然我们能够在一个slice中实现两个MUX8,我们理论上就可以做到MUX16,事实也确实如此。

每个slice还就有一个F8MUX,它可以把F7AMUX和F7BMUX的输出作为自己的输入,形成一个多达27个输入(或一个16:1的MUX)的组合函数。一个slice中最多只能部署一个MUX16。

理论上我们时可以在多个SLICEM中部署出超过MUX16的MUX的,但是在SLICE之间没有直接的连接来帮助我们构成这样的大规模MUX。

其实大家不难发现,我们在slice中实现MUX,最基本的就是依靠LUT,当一个LUT不够满足我们的需求的时候,就通过fpga中的MUX把LUT两两组合起来构成更大规模的MUX。这样设计的一大好处就是可以使得整体的结构具有对称性,这样各个模块之间走线的延迟可以尽可能趋于一致,可以避免很多时序上的问题。

三、小结

通过本文,我们知道了在fpga中实现MUX时可以使用的资源有MUX和LUT,但是还有一个问题,既然我们可以用LUT来实现MUX的功能,为什么不直接全部采用LUT呢,例如MUX8可以用2个LUT+一个MUX实现,理论上也可以用2个LUT+1个LUT实现。文章来源:https://www.toymoban.com/news/detail-721159.html

之所以在fpga中还保留MUX这个设计,首先就是成本问题。MUX在数字电路中的使用频率是很高的,而MUX器件是一种晶体管较少的逻辑单元,通常查找表存储逻辑函数所需的逻辑资源以及控制连接的存储单元要消耗大量的晶体管,所以MUX在这方面有着巨大的优势。同样的用LUT来实现MUX也会造成资源的浪费。文章来源地址https://www.toymoban.com/news/detail-721159.html

到了这里,关于FPGA原理与结构(4)——数据选择器MUX(Multiplexers)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!