一.半加器及全加器原理

1.半加器

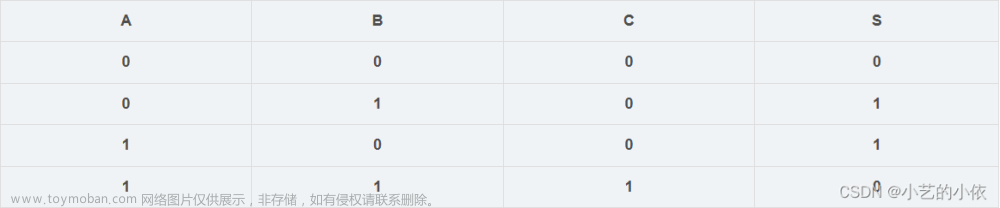

- 真值表

| A | B | C0 | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

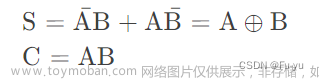

- 表达式

S=A⊕B

C=AB

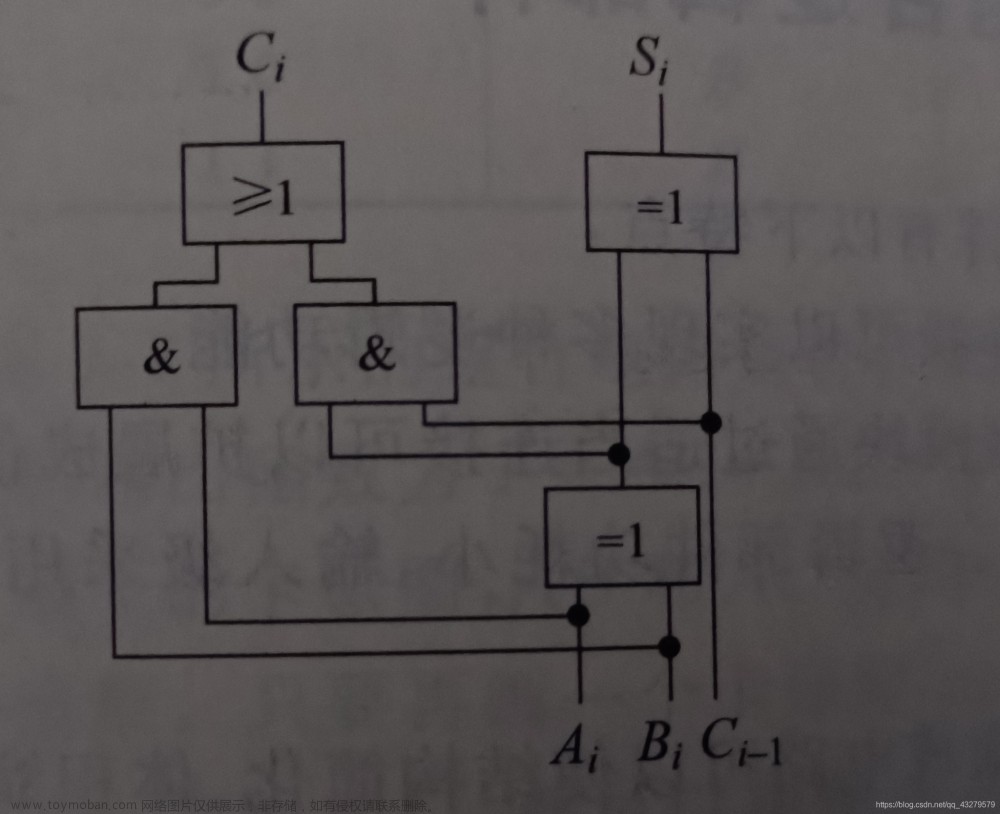

2.全加器

- 真值表

| ain | bin | cin | cout | sum |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

- 表达式

Sum=Ain⊕Bin⊕Cin

Cout=(Ain⊕Bin)⋅Cin+AinBin=(Ain&Bin)∣(Bin&Cin)∣(Ain&Cin)

二.原理图实现1位加法器

1.创建项目

-

选择File->New Project Wizard

-

设置项目路径和项目名

-

按个人需求选择芯片

2.半加器原理图输入

-

选择File->New->Block Diagram/Schematic File

-

选择元件(一个and2,一个xor,两个input,两个output)

-

原理图如下

-

编译成功后选择tool->Netlist Viewers->RTL Viewer

-

得到电路图如下

-

选择File→New->VWF

-

按如下操作添加信号

-

配置信号前需要做如下配置(tool->launch simulation library complier)

-

编辑信号并仿真

-

仿真效果如下

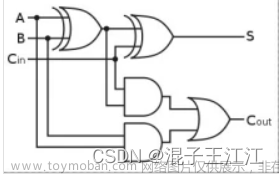

3.全加器原理图输入

-

选择File->Create/Update->CreateSymbolFilesforCurrentFile

-

选择File->New->Block Diagram/Schematic File

-

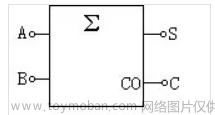

选择元件(两个halfadder,一个or2,三个input,两个output)

-

原理图如下

-

注意在此处需要先将fulladder置顶(Project->Set as Top-Level-Entity)再进行编译

-

电路图如下

-

编辑信号并仿真

-

仿真效果如下

三.Verilog实现1位加法器

-

创建Verilog文件

-

代码如下

module full_adder(

//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位

input ain,bin,cin,

//输出信号,cout表示向高位的进位,sum表示本位的相加和

output reg cout,sum

);

reg s1,s2,s3;

always @(ain or bin or cin) begin

sum=(ain^bin)^cin;//本位和输出表达式

s1=ain&cin;

s2=bin&cin;

s3=ain&bin;

cout=(s1|s2)|s3;//高位进位输出表达式

end

endmodule

-

注意编译时需要保证模块名和文件名一致,不然会报错

-

电路图如下

-

选择File→New->VWF

-

编辑信号并仿真

-

仿真结果如下

四.下载到开发板有关操作

-

Pin Planner中配置引脚

-

Programmer中下载

- 效果如下

五.总结

上学期接触了FPGA开发,但是由于假期重做系统,重新下载的quartus和modelsim,本文中quartus和modelsim都是用的13.1版本。本次实验出现了一些错误,包括破解失败导致无法运行quartus相关文件,包括EDA实现quartus和modelsim自动仿真时参考教程学习,Verilog实现1位全加器时模块名和文件名不一致导致的报错,参考学长学姐的博客都得到了解决,这次实验是FPGA较为初级的操作。仍需进一步学习,后期会定期更新有关FPGA的博客。文章来源:https://www.toymoban.com/news/detail-721204.html

六.参考博客

https://blog.csdn.net/qq_43279579/article/details/115158140

https://blog.csdn.net/qq_43279579/article/details/115176423

https://blog.csdn.net/qq_43279579/article/details/115480406文章来源地址https://www.toymoban.com/news/detail-721204.html

到了这里,关于Quartus实现一位全加器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!