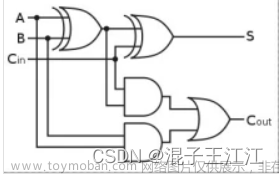

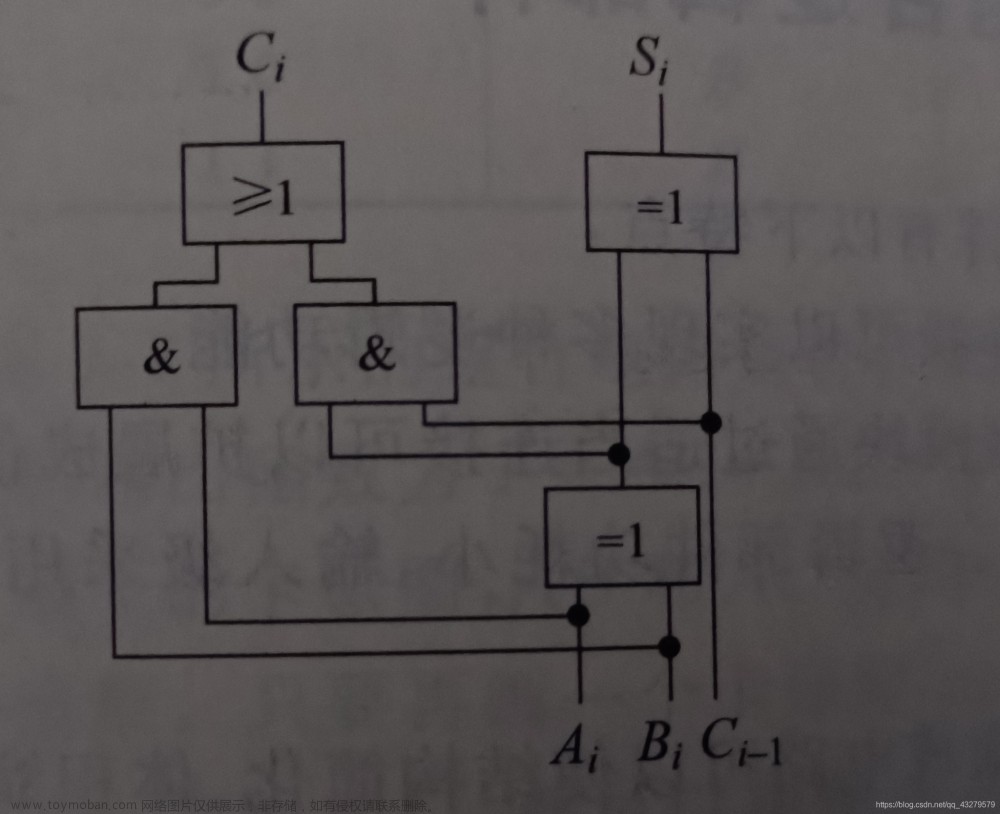

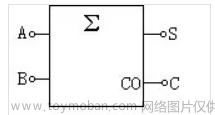

一.原理图实现四位全加器

-

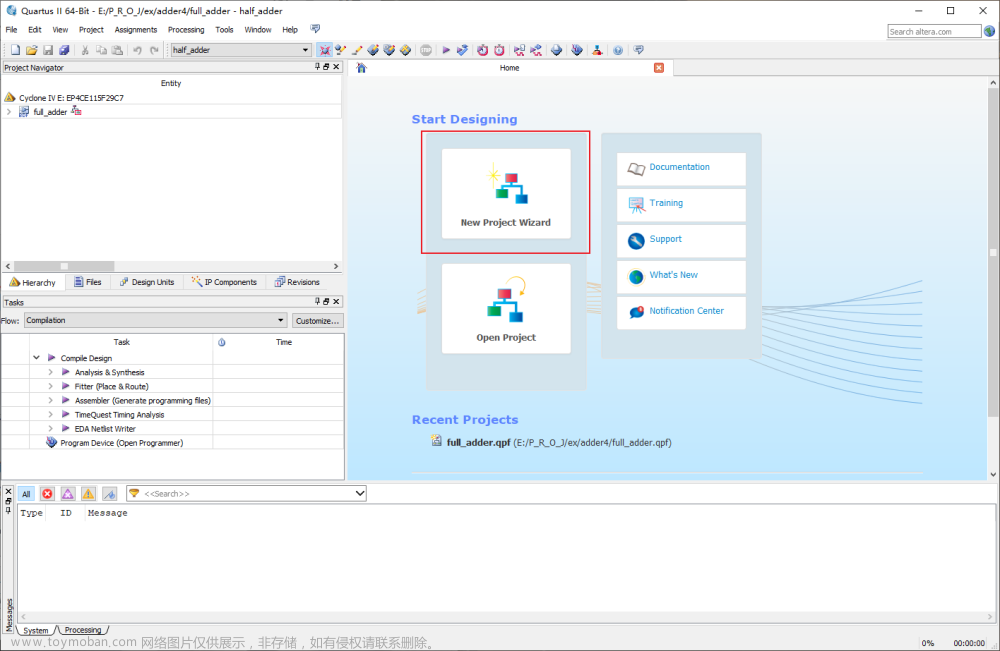

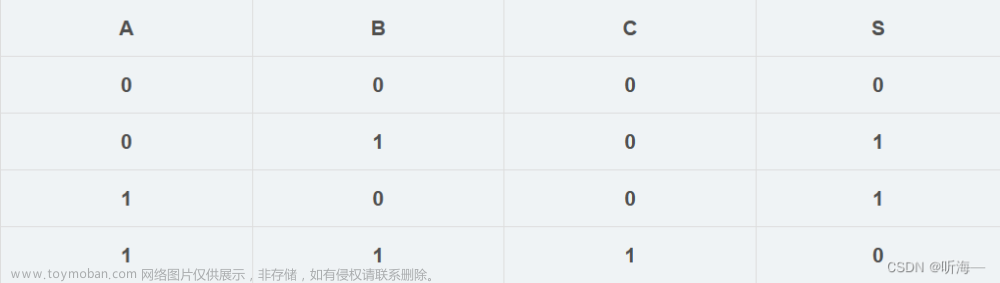

1.首先将之前做的一位全加器作为模块选择File->Create/Update->CreateSymbolFilesforCurrentFile

-

选择File->New->Block Diagram/Schematic File

-

选择元件(四个fulladder,两个input,两个output,两个gnd)

-

原理图如下(注意标注输入输出名和分支名)

-

编译成功后选择tool->Netlist Viewers->RTL Viewer得到电路图如下

-

选择File→New->VWF

-

按如下操作添加信号

-

编辑信号并仿真

-

仿真结果如下

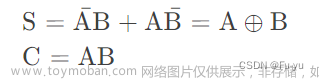

二.Verilog实现四位全加器

-

创建Verilog文件

-

代码如下

module four_bit(a,b,cin,cout,dout);

//与保存的文件名相同,但尽量不与之前的原理图名相同

input [3:0] a,b; //a,b为4位输入

input cin;

output cout;

output [3:0] dout;

assign {cout,dout} = a+b+cin; //a+b 加法操作

//使用拼接运算符将cout、dout拼接,dout取结果中的低四位

endmodule

-

电路图如下

-

按如下操作添加信号

-

编辑信号并仿真

-

仿真结果如下

三.引脚配置及效果

-

引脚配置

-

效果如下

四.总结

四位全加器是在一位全加器基础上实现的,本文省略了一些步骤,详情可以参考笔者一位全加器的博客。出现的问题有需要置顶文件再编译,Verilog实现需要模块名和文件名保持一致,Verilog实现和原理图实现的项目名要保证不一致,不然会报错。文章来源:https://www.toymoban.com/news/detail-721370.html

五.参考博客

https://blog.csdn.net/qq_53203987/article/details/129738856?spm=1001.2014.3001.5501

https://blog.csdn.net/XiaoYiDeXiaoYi/article/details/129716957?spm=1001.2014.3001.5502文章来源地址https://www.toymoban.com/news/detail-721370.html

到了这里,关于# Quartus实现四位全加器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!