报错类型:

Error: (vsim-19) Failed to access library "cyclone_ver" at "cyclone_ver".

报错原因:

库文件未能加载到指定文件夹。

解决办法:

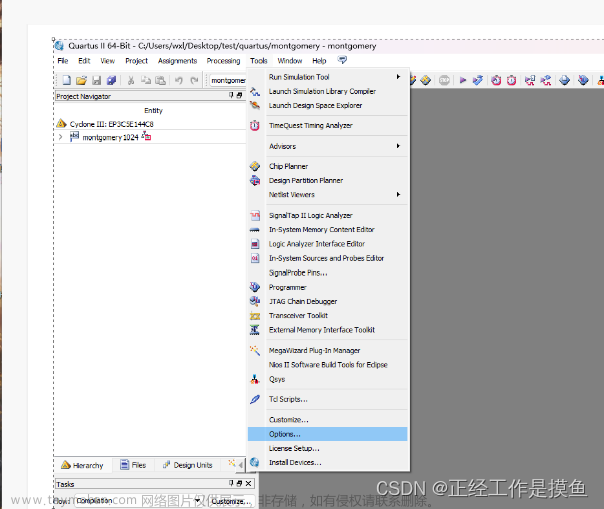

①点击顶部菜单栏得“Tools”选项;

②再选择“Launch Simulation Library Compiler”;

③底部“Output directory”这里选择 ‘simulation’ 文件夹下的 ‘qsim’ 文件夹;

④然后点击“Start Compilation”,等待成功后,重新运行VWF文件即可。

步骤截图:

①②

文章来源:https://www.toymoban.com/news/detail-721629.html

③④

文章来源地址https://www.toymoban.com/news/detail-721629.html

到了这里,关于Quartus II 13.1——VWF文件 仿真报错的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!