verilog学习笔记(一)

模块结构

第一部分(必填)

module 模块名 ([端口列表]);

[端口信号声明;]

[参数声明;]

1、模块名是指电路的名字,由用户指定,最好与文件名一致

2、端口列表是指电路的输入/输出信号名称列表,信号名由用户指定,各名称间用逗号隔开。

3、端口信号声明是要说明端口信号的输入输出属性、信号的数据类型,以及信号的位宽。

输入输出属性有input,output,inout(双向)三种

信号的数据类型常用的有wire和reg两种

信号的位宽用[n1:n2]表示

同一类信号之间用逗号隔开

参数声明要说明参数的名称和初值

例子:

例子解释:

1、位宽不作说明,则默认1位;

数据类型不作说明,则默认为wire型。

2、输出信号S位宽为4位,对应信号为S[3],S[2],S[1],S[0]

第二部分功能描述部分

内部信号声明

(常用语句只有3种:assign语句,always语句,底层模块调用语句)

底层模块或门原语调用(包括生成块)

initial 或always语句块

任务和函数定义

specify块(路径延迟)

第三部分结束语句(必填)

endmodule

常用语句

assign语句(连续赋值语句)

基本格式

assign 赋值目标 = 表达式

特点“

1、赋值目标必须是wire型,wire表示电路间的连线。

2、之连续赋值语句是指其总是处于激活状态,只要表达式中的操作数有变化,立即进行计算和赋值。

例子

assign M=B|C;

Verilog具有丰富的表达式运算公式,可用于assign语句

算术型

(记住%求余,**求幂)

注意:

1、除了求余的操作数只能是整数,其它的操作数可以是实数也可以是整数。

2、求余运算结果取第一个操作数的符号

逻辑型

注意:

1、逻辑型运算的结果由3中1(真),0(假)、x(不确定)。

关系运算符

运算就结果与逻辑运算相同

按位运算符

注意:

1、按位运算的操作数是1位或多位二进制数。

2、按位非的操作数只有一个,将该数的每一位求非运算。

3、其它按位运算的操作数有2个或多个,将两个操作数对应的位两两运算;如果操作数位宽不同,位宽小的会自动左添0补齐;

4、结果与操作数位宽相同;

5、注意与逻辑运算符区分:

&按位与,&&逻辑与;

|按位或,||逻辑或。

缩减运算符

说明:

1、与按位与运算&区分:

例子:

(按位与运算)

Y=4‘ b1001&4’b0111结果为0001

(缩减与)

Y=&4‘ b1001结果为0

可以看出&起作用的运算位置不同

2、计算过程:

以上面的例子为例:从左到右第一位与后一位作与运算,求得的结果又与后一位作运算,结果只有一位

3、缩减运算的操作数是1位或多位二进制数

移位运算符

格式

操作数 移位符 n;

注意:

1、只有对有符号数的算术右移自动补符号位;其他移位均自动补0。

2、移位符与算术移位符的区别

例:

Y=4’b1001>>1;结果0100

Y=4’b1001>>>1;结果1100

拼接复制运算符

格式:

1、{操作数1,操作数2,…}

将操作数1,2…拼接到一起。

2、{n{操作数1,操作数2,…}}

将操作数1,2…拼接到一起后复制n遍拼接起来。

条件运算符

?:用于条件赋值

格式:

表达式1?表达式2:表达式3

always语句块(也叫过程块)

基本格式:

always @(敏感信号条件表)

各类顺序语句;

注意:

1、always语句本身不是单一的有意义的一条语句,而是和下面的语句一起构成一个语句块,称之为过程块;过程块中的赋值语句称过程赋值语句;

2、该语句块不是总处于激活状态,当满足激活条件时才能被执行,否则被挂起,挂起时即使操作数有变化,也不执行赋值,赋值目标值保持不变;

3、赋值目标必须是reg型的。

4、always语句中还可以使用if、case、for循环等语句,其功能更加强大。

5、激活条件由敏感信号条件表决定,当敏感条件满足时,过程块被激活。

敏感条件有两种,一种是边沿敏感,一种是电平敏感。

边沿敏感:

(posedge 信号名) 信号上升沿到来

(negedge 信号名) 信号下降沿到来

电平敏感:(信号名列表)信号列表中的任一个信号有变化

例:

(a,b,c)当a,b,c中有一个发生变化

例:

always@(posedge CLK)

Q=D;

当CLK上升沿到来时,激活该语句块,将D的值赋给Q;

否则,该语句块挂起,即使D有变化,Q的值也保持不变,直到下一次赋值。

此语句相当于一个D触发器

例:

always@(D)

Q=D;

当D有变化时(不管是由1变0还是由0变1),激活该语句块,将D的值赋给Q;否则,该语句块挂起,Q的值保持不变,直到下一次赋值。

相当于二极管

在以上两个例子中Q必须是reg型的

与assign语句相比:

1、always语句块中除了可以使用表达式赋值以外,还可以使用if,case等行为描述语句,还能够描述边沿变化,因此其功能比assign语句更强大(assign语句不能使用if等语句,也不能描述边沿变化)。

2、always语句块中如果多条就值语句必须将其用begin end包括起来,assign语句中没有begin end。(verilog语言所有是并行执行的,但是begin end里面是顺行执行的)

3、同一程序的always和assign两条语句,他们之间是并行的。如果程序中有一个变量Q则要进行声明。

内部信号声明格式:

数据类型 位宽 信号名称 元素个数

阻塞赋值与非阻塞赋值

设A、B同时由0变1

激活前:M1=0,M2=0,Q=0

阻塞赋值例子:

条件:

激活后:M1=1,M2=0,Q=1(每一步计算之后马上赋值)

非阻塞赋值例子:

激活后:M1=1,M2=0,Q=0(计算全部完成之后再赋值)

注意:

1、阻塞赋值用的符号是=,非阻塞赋值用的符号是<=

2、设计组合电路时常用阻塞赋值,设计时序电路时常用非阻塞赋值(但不是绝对的)。

3、不能在一个always块中混合使用阻塞赋值和非阻塞赋值。

底层模块和门原语调用

底层模块

底层模块描述

顶层模块描述:

为了调用底层模块,需要加两个内部变量d1和q1;并给两次调用的模块进行命名;调用时例化名不能省略。

底层模块调用格式:

底层模块名 例化名 (端口映射)

端口映射有两种方法:

端口名关联法(命名法)

位置关联法(顺序法)

命名法格式:

(.底层端口名1(外接信号名1),.底层端口名2(外接信号名2),…)

以上例的底层模块调用为例:

DFF dff1(.CLK(clk),.D(d1),.Q(q1));

因为有名字对应,不必按底层模块的端口信号列表顺序

顺序法格式:

(外接信号名1,外界信号名2,…)

DFF dff2(q1,d,q);

必须严格按照底层模块的端口信号列表顺序书写

门原语调用

门原语调用格式:

门原语名 实例名 (端口连接)

其中实例名可省略(和模块调用不同),端口连接只能采用顺序法,输出在前,输入在后。

常见的门:

Verilog中的数据类型

Verilog中的数据类型分为两大类

线网类(net类)

最常用的是wire

变量类(variable类)

最常用的是reg

因连续赋值语句不需要保存,过程赋值语句后者需要保存。

因此规定:

数据类型net型用于连续赋值的赋值目标或门原语的输出,且仿真时不需要分配内存空间

数据类型variable用于过程赋值的赋值目标,且仿真时需要分配内存空间。

数据类型使用注意

1、使用何种赋值语句对该信号进行赋值,如果是连续赋值或门原语赋值或例化语句赋值,则定义成net型;如果是过程赋值则定义成variable型。

2、对于端口信号来说,input信号和inout信号必须定义成net型的;output信号可以是net型的也可以是variable型的,决定于如何对其赋值。

三种赋值方法比较:

(1)使用连续赋值

此时,d和e必须定义为net型

(2)使用门原语赋值

此时,d和e也必须定义为net型的。

(3)使用过程赋值语句

此时,d和e必须定义为variable型的。

Verilog数字的表示格式

无符号数的表示方法:

<位宽>’ <进制><数字>

例:

2‘ b00——(00)2

有符号数的表示方法:<位宽>’ < sb ><数字>

例:

8’ sb10111011——(-69)10

注意有符号数是按照补码表示的,即第一位是符号位。(1表示负数,0表示正数)

Verilog语言的逻辑值有四种

1:逻辑1,高电平,数字1

0:逻辑0,低电平,数字0

x:不确定

z:高阻态

if语句

判断执行结果:

结果为真(1或非0),则执行真语句,

条件为假(0或x),则执行假语句。

在用if语句设计“组合电路”时要注意,如果条件不完整,会综合出寄存器。

使条件完整的两种方法:

1、加else

2、设初值

case语句

注意

Case语句最后要有个endcase不能忘。

如果条件描述不完整,则会综合出寄存器;在设计组合电路时要注意使条件描述完整。

加default语句可以使条件完整。如果条件描述完整也可以不加default语句。

Verilog语言的描述风格

三种描述方式

1、结构化描述(也称门级描述)(全部用门原语和底层模块调用)(不适合具体书写,因为不是很直观)

2、数据流级描述(全部用assign语句)

3、行为级描述(全部用always语句配合if、case语句等)

4、RTL级描述(数据流级+行为级,可综合)

实际描述是三种混合的。

其它规定

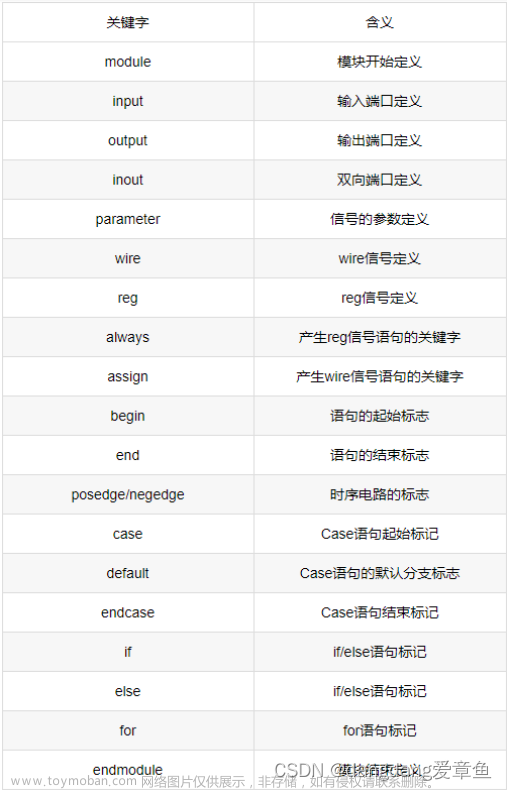

(1)关键字

关键字即Verilog语言中预定义的有特殊含义的英文词语

(2)标识符

标识符即用户自定义的信号名、模块名等等;注意关键字不能作标识符;Verilog区别大小写(关键字都是小写)。

(3)文件取名和存盘

Verilog文件扩展名为.v; verilog不要求文件名和模块名一致,但Quartusll要求一致

(4)注释

//单行注释

/**/多行注释

数字电路遗忘知识点的补充

常见的电路门 文章来源:https://www.toymoban.com/news/detail-722892.html

文章来源:https://www.toymoban.com/news/detail-722892.html

参考b站BV1iv4y1F7Km文章来源地址https://www.toymoban.com/news/detail-722892.html

到了这里,关于verilog入门学习笔记的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!