目录

MIG整体介绍

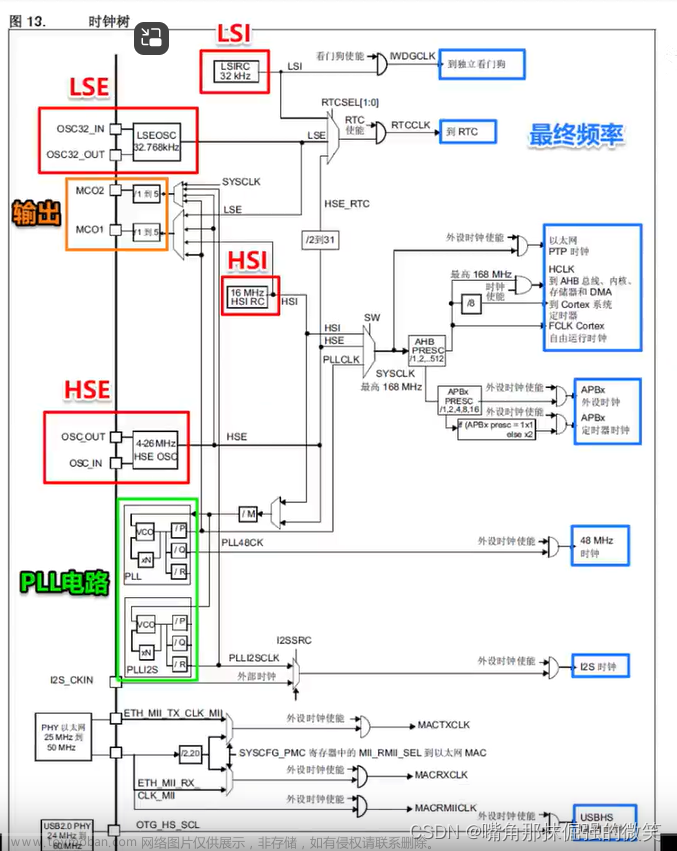

MIG的时钟架构

MIG配置过程中时钟的含义和设置

Clock Period

PHY to Controller Clock Ratio

VCCAUX_IO

Input Clock Period

System Clock

Reference Clock

MIG整体介绍

MIG的时钟架构

从上面的时钟架构中,可以看出,有以下几种时钟:

| 时钟名称 |

方向(相对于MIG) |

说明 |

| reference clock |

输入 |

供idelayctrl使用,通常需要200MHz,可以外部提供(single-end,differential),也可以内部提供(no buffer,use system clock)。 对DDR频率>667MHz时,参考时钟需要300/400MHz(也可从内部产生) |

| system clock |

输入 |

mig的系统时钟(主时钟),可以外部提供(single-end,differential),也可以内部提供(no buffer)。 |

| ui_clk |

输出 |

供用户接口端使用,对应图中的internal (FPGA) logic clock,具体时钟频率,由PHY to Controller Clock Ratio决定(4:1 or 2:1) |

| ICLK/ICLKDIV |

输出+供MIG内部使用 |

Read Path (Input) I/O Logic Clock,由PHASER_IN根据外部DQS产生,供内部采样输入的iserdes数据使用 |

| OCLK/OCLKDIV |

输出+供MIG内部使用 |

Write Path (Output) I/O Logic Clock,由PHASER_OUT产生,供产生输出地址/控制+数据的时钟,以及外部的CK和DQS |

MIG配置过程中时钟的含义和设置

Clock Period

operating frequency for all of the controllers,指控制器controller与DDR之间的数据访问时钟,X2就是数据速率

PHY to Controller Clock Ratio

- the ratio of the physical layer (memory) clock frequency to the controller and user interface clock frequency。比如下图中,4:1,对应控制器controller的时钟是400MHz,用户接口ui的时钟是100MHz

- The 2:1 ratio has lower latency. The 4:1 ratio is necessary for the highest data rates

VCCAUX_IO

- 2.0V is required at the highest frequency settings in the High Performance column

- Either 1.8 or 2.0V can be used at lower frequencies

Input Clock Period

The desired input clock period is selected from the list. These values are determined by the memory clock period chosen and the allowable limits of the parameters

指的就是时钟架构种的系统时钟sys_clk,对于mig来说就是input clock

文章来源:https://www.toymoban.com/news/detail-723695.html

文章来源:https://www.toymoban.com/news/detail-723695.html

System Clock

- No Buffer scenarios, sys_clk_i signal needs to be connected to an internal clock

- 在block design的设计中,因为sys_clk使用内部时钟(即clk_wiz倍频出),所以使用no buffer

- 这里和上一页的Input Clock Period其实是指的一个时钟,上一页选择频率,这一页选择输入方式,可以外部提供(single-end,differential),也可以内部提供(no buffer)。

Reference Clock

- The Use System Clock option appears when the input frequency is between 199 and 201 MHz (that is, the Input Clock Period is between 5,025 ps (199 MHz) and 4,975 ps (201 MHz)。

- 即系统时钟200MHz时,可以选择use system clock

文章来源地址https://www.toymoban.com/news/detail-723695.html

文章来源地址https://www.toymoban.com/news/detail-723695.html

到了这里,关于【逻辑学习笔记】MIG中各种时钟的含义和如何设置的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!