- 实验目的

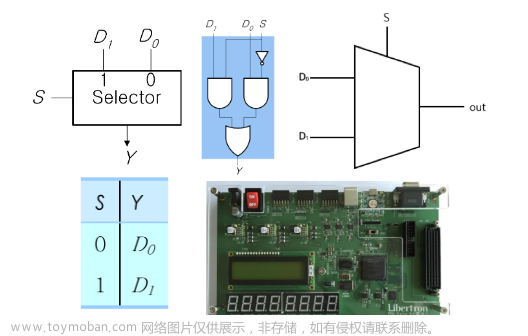

实现一个多路选择器,进行“2选1”。也就是对2个信号进行1个特定条件的筛选,满足这个特定条件的话,其中一个的数值或信息就成为输出信号的数值或信息。不满足此条件的,就输出另一个信号的数值和信息。

- 实验原理

- 理论原理

2个输入信号,选择其中一个作为输出。本项目当中,有输入信号in_1和in_2。当选通信号sel为高电平的时候,输出in_1;当选通信号sel为低电平时,输出in_2。

- 硬件原理

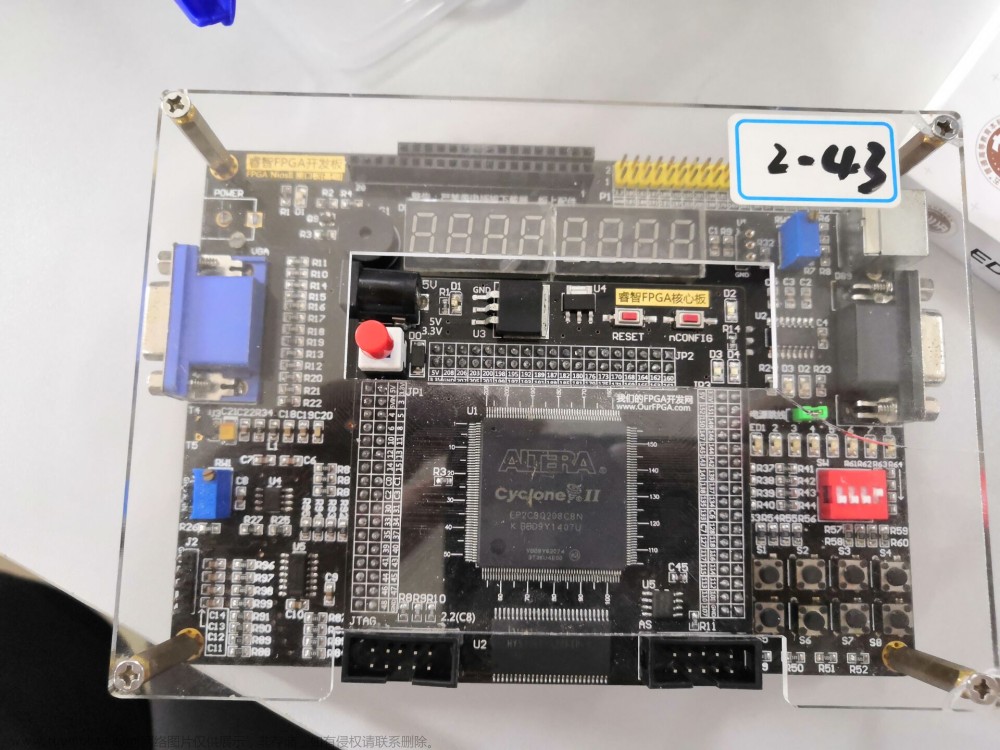

硬件使用: 按键3个,led灯1个。

原理设想: 通过硬件设施来具体表现。Key1的按下,代表in_1输入高电平,反之意味着输入低电平。Key2按下,代表in_2输入高电平,反之意味着输入低电平。同理,key3就代表了选通信号sel。按下是高电平,不按是低电平。输出信号就拿LED灯表示,通过亮灭来代表输出信号的情况。

按键:按下导通。

LED:高电平导通,输入高电平,LED灯亮。

- 系统架构设计

思路:抓住要实现的的功能,就是“判断、筛选”。那就只要一个“筛选模块”。对谁筛选呢?对输入信号当中的两个信号(in_1和in_2)进行筛选。那么要进行怎么样(什么条件的筛选呢?),条件就是所谓的选通信号sel。完整的筛选条件,就是“sel为高电平时候,输出in_1的数值或信号;sel为低电平时,输出in_2的数值或信号”。

类比推理:举个例子,选择今天中午做啥饭。Sel这个选通信号,就如同我们的大脑,大脑(sel)告诉我,想吃米了。面前既有米袋子(in_1),又有面袋子(in_2)。那么得出结论(out):今天做米饭(in_1的数值或信号)。反之亦然。

所以系统架构设计就很简单,三个输入,进入判断模块,一个输出。输入分两大类:两个具体输入信号in_1和in_2,一个选通信号sel。

- 模块说明

- 模块端口信号列表

In_1:输入信号,用按键key1控制,按下为高电平

In_2:输入信号,用按键key2控制,按下为高电平

Sel:选通信号,用按键key3控制,按下为高电平。当然也是输入的信号。

out:输出信号,用LED灯控制,高电平点亮,灭了就是低电平。

- 状态转移图

文章来源地址https://www.toymoban.com/news/detail-726493.html

- 时序图(箭头是为了对齐,便于观察)

三个输入其实都是随机的,也就是说,想啥时候拉高拉低(想啥时候输入,想啥时候输出都无所谓)。但是有个小漏洞:并没有明确限定和说明,一次性同时到底能按几个按键。默认设定是一次最多就按下2个按键(按KEY3选通信号和KEY1;按KEY3和KEY2;单独按KEY1;单独按KEY2)甚至没规定按键一个都不按下的情况时,LED灯的亮灭情形。

对于三个输入信号(in_1/in_2/sel)按键的按下,信号电平拉高。按键松开,电平拉低。明确一点,按下和松开,都是随意的。选择的条件是什么?是sel要是高电电平的大前提下:①输入in_1是高,输出out则高,LED亮;②输入in_2是高,此时输出没做安排,这也是个漏洞。输出无法判断。

Sel要是在低电平的大前提下:输入in_2是高,输出out高,LED亮。

但是漏洞仍旧存在。

- 仿真波形图

其实波形图目前感觉就是和当初画的时序图对比一下,一样说明咱对了。但是我发现个小技巧,当你看不懂波形图或者波形图太复杂,看看算式,咱们数形结合。方便理解加深印象。

注意这个栏目,它可以把波形图和仿真的结果按照算式的方式表达(目前本项目是这样的)然后结合我们当时的设计思路和时序图对比一下,估计就出来了。

注意这个栏目,它可以把波形图和仿真的结果按照算式的方式表达(目前本项目是这样的)然后结合我们当时的设计思路和时序图对比一下,估计就出来了。

- 代码编写及其思路

文章来源:https://www.toymoban.com/news/detail-726493.html

仿真:

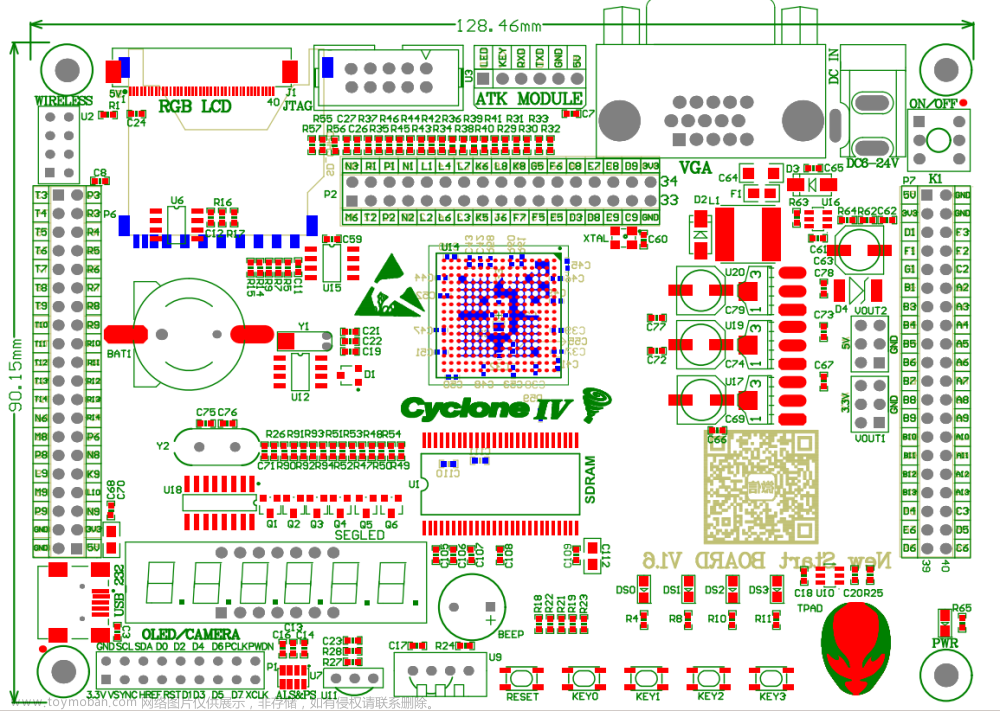

代码敲完以后,就用Q进行工程操作。新建——C4,256-8—添加代码—点编译。到了这个情况后,准备仿真

仿真:

仿真必须写仿真代码。点到tb 文件夹里。建立仿真代码的.v文件

对于仿真代码:(仿真文件就是要对我们被仿真的信号进行一个模拟)

`timescale 它是关键词时间尺度(英文time是时间,scale是大小、规模、尺度的意思)

在仿真文件当中,begin-end当中的语句都是顺序执行的。在没有延时的情况下,几乎是没有差别的。在RTL代码当中,begin-end相当于一对{ }的作用。在同一个always块当中,如果给多个变量赋值,要使用begin-end。

此处使用initial语句,是为了给in_1,in_2,sel进行一次初值的赋值操作。

对于要使用的initial语句,他的结构上是:

然后这里,对于#就是延时的意思,10就是10纳秒

然后这里,对于#就是延时的意思,10就是10纳秒

绑定管脚:输入信号in_1,就认为是KEY1,E15

In_2是KEY2,E16

输出out就是LED1,F16

选通信号sel,应该是KEY3,M16

仿真代码:

到了这里,关于FPGA的verilog关于多路选择器(2选1)的设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!