基于FPGA的高速数据采集ATA接口Verilog开发与Matlab

摘要:

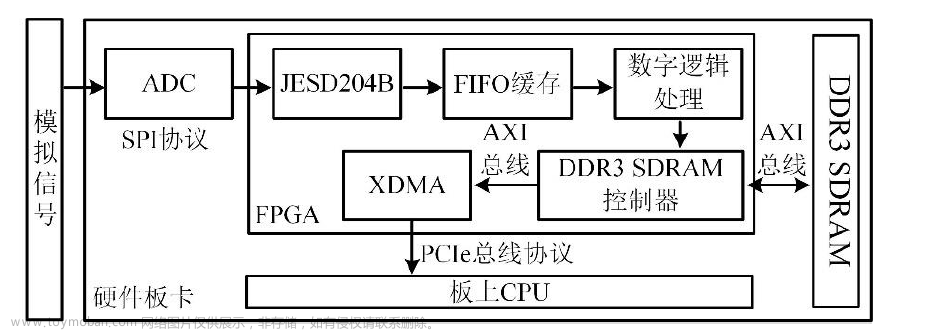

本文介绍了基于FPGA的高速数据采集ATA接口的Verilog开发与Matlab的应用。通过使用Verilog语言进行FPGA的硬件设计,实现了ATA接口的数据采集功能。同时,结合Matlab进行数据处理和分析,实现了对采集的数据进行实时处理和显示。文章中将详细介绍Verilog代码的实现过程,以及Matlab的数据处理和分析方法。

-

引言

随着数据采集和处理的需求不断增加,基于FPGA的高速数据采集系统得到了广泛的应用。ATA接口作为一种常见的数据传输标准,具有高速传输、稳定性好等特点,被广泛应用于存储设备和数据采集领域。本文将结合Verilog开发和Matlab应用,实现基于FPGA的高速数据采集ATA接口的设计与实现。 -

ATA接口的Verilog设计

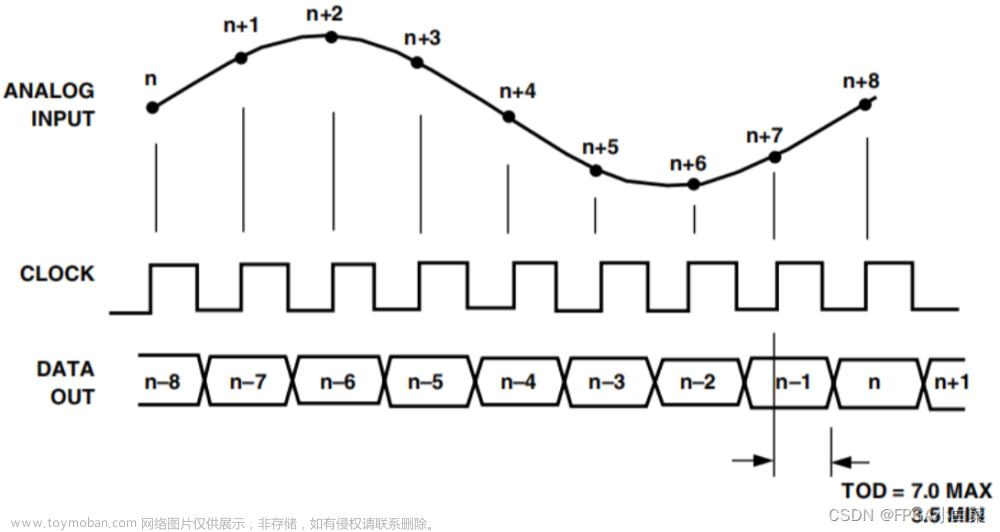

ATA接口的设计主要包括接口的硬件设计和数据传输的控制逻辑。在Verilog中,我们可以使用模块化的方式对ATA接口进行设计。

首先,定义ATA接口的输入和输出端口,包括数据线、地址线、控制线等。然后,根据ATA接口的协议规范,编写数据传输的控制逻辑。控制逻辑包括状态机的设计、数据传输的时序控制等。最后,根据实际需求,对接口进行适当的扩展和优化。文章来源:https://www.toymoban.com/news/detail-726833.html

下面是一个简化的ATA接口的Verilog代码示例:文章来源地址https://www.toymoban.com/news/detail-726833.html

module ATA_interface (

input wire clk,

input wire reset,

input wire [7:0] data_in,

output wire [7:0] data_out,

input wire [3:0] address,

input wire read_enable到了这里,关于基于FPGA的高速数据采集ATA接口Verilog开发与Matlab的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!