萌新的SOC学习之重新起航SOC

ZYNQ PL 部分等价于 Xilinx 7 系列 FPGA

PS端:Zynq 实际上是一个以处理器为核心的系统,PL 部分可以看作是它的一个外设。

我们可以通过使用AXI(Advanced eXtensible Interface)接口的方式调用 IP 核,系统通过 AXI 接口将 IP 与处理器连接,也就是实现 PL 与 PS 互联。Zynq-7000 系列的亮点在于它包含了完整的 ARM 处理器系统,且处理器系统中集成了内存控制器和大量的外设,使 Cortex-A9 处理器可以完全独立于可编程逻辑单元。实际上在 Zynq 中,PL 和 PS 两部分的供电电路是独立的,这样 PS 或 PL 部分不被使用的话就可以被断电。

我们从PS的最小系统出发了解整个体系结构

我们从基本的hello 出发

对于创建的IP核经过删减只留下了

一个是DDR 另一个是UART的串口

对于PS端 只要点击 generate output products 它会自动帮我们进行管脚分配

然后点击 create HDL Wrapper 为我们的设计生成一个硬件描述文件的顶层文件

这是用verilog语言写下来的

现在硬件的搭建已经结束了

我们现在来看整体结构

因为我们并不需要PL端 所以就不需要生成比特流文件了

硬件的最后一步直接导出到SDK

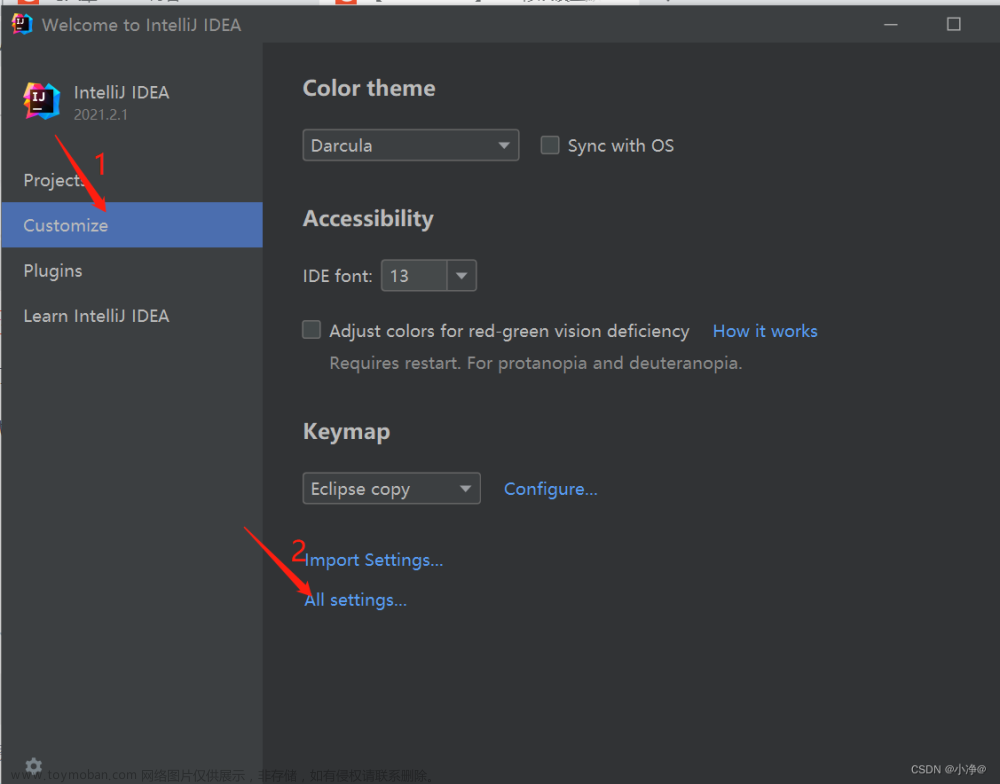

接下来的SDK就是软件开发环境

应用软件会在硬件上执行

ok掌握了最最最基础的SOC逻辑

我们投入更加多的设计

接下来我们学习 GPIO之MIO控制LED实验

我们从GPIO这部分了解到了PS PL的内容包含

PS包含了 processing System

1.APU

2.Memory interfaces

3.I/O peripherals

4.Interconnect

PL–FPGA文章来源:https://www.toymoban.com/news/detail-727024.html

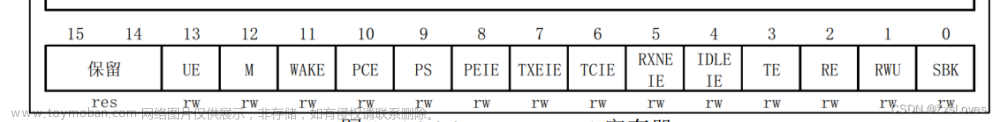

GPIO是一个外设用来对器件的引脚作观测和控制

MIO模块 实现多路复用的效果文章来源地址https://www.toymoban.com/news/detail-727024.html

到了这里,关于【【萌新的SOC学习之重新起航SOC】】的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!