一、 前言

- 在电脑上安装虚拟机或者找一个电脑安装linux,用于编译petalinux工程;

- 安装与vivado对应的petalinux-tool;

- 版本信息:

1)linux:ubuntu16.04.06;

2)vivado:v2021.1;

3)petalinux:v2021.1;

4)petalinux工程参考bsp:xilinx-zc702-v2021.1-final.bsp; - vivado可以在linux中,也可在windows中;

- 离线编译包下载,在petalinux工具下载界面下面就有下载链接,如果是zynq需要下载sstate_arm_2021.1(5.5G),如果是zynqMP需要下载sstate_aarch64_2021.1(12.7G),另外还需要下载文件系统Downloads(42.7G);

- 感谢 https://www.freesion.com/article/25851500179/ 解决了我的关键性地址分配问题。

二、 设计流程

- 导出.xsa文件

新建vivado工程,勾选zynq最小系统模块,此处官方建议最小系统需要有如下模块:

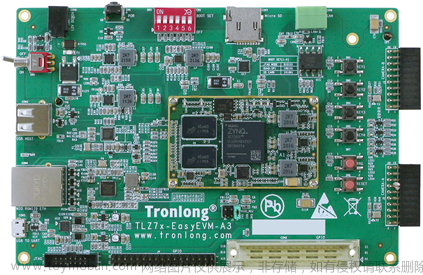

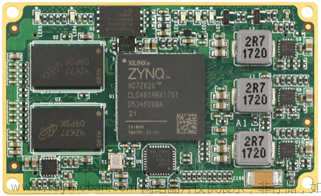

本人使用之前的板卡做测试,由于板卡串口是连接在PL侧,所以本次验证还需要fpga的bit文件,如果所有的输出引脚都在PS侧,可以不用fpga的bit文件,blockdesign如下:

- 新建petalinux工程

ubuntu中新建文件夹,依据官方提供的bsp包新建工程,命令如下:

//导出petalinux工具的环境变量,注意source只对本终端有效

source ~/tools/01_petalinux/v2021/settings.sh

//依据bsp包新建工程

petalinux-create –t project –s ./xilinx-zc702-v2021.1-final.bsp –n petalinux_from_bsp1

//进入工程目录

cd petalinux_from_bsp1 - 配置petalinux工程

1)导入.xsa文件

petalinux-config –get-hw-description …/cpu_wrapper_20230413.xsa

回车,调出工程配置界面如下:(键盘上下左右键控制设置)

2)进入“Subsystem AUTO Hardware Settings”

注意:此界面与v2019版及之前的版本不同,缺少了Advanced Bootable Images Storage Settings,问题不大,缺少有缺少的做法

进入Flash Settings,默认配置如下:

修改如下:

解释:

a) boot:大小设置为10MB,这个跟后面封装的fsbl、u-boot、bit文件大小有关,默认是5MB,有点小,本人测试时u-boot启动一直有问题,就是因为我的BOOT.bin是5.1MB,这里使用了默认配置,导致一直失败;

b) bootenv:这里没有用到,但是不能删掉,保留,但是大小设置成64KB(flash最小读写扇区);

c) kernel:这里指的是petalinux工程编译后生成的image.ub,对应于fit image,大小设置为21MB;

d) bootscr:这是v2020以后的petalinux版本才用到的,用于引导u-boot的,具体还不太懂,里面内容不多,大小设置为64KB即可;

3)进入“u-boot Configuration”–>“u-boot script configuration”–>“QSPI/OSPI image offsets”

将fit image offset设置为0xA10000,原因是flash中配置时boot+bootenv=0xA10000

将fit image size设置为0x1500000,与flash中的配置一致;

4)进入Yocto Settings,设置离线编译库文件路径

说明:

a) petalinux默认是在线编译,因为服务器在国外,首次编译时会比较慢,而且可能会失败,因此提前下载离线编译库文件使用离线编译效率比较高,但是提前下载的库文件较大,在petalinux工具下载界面下面就有下载链接,如果是zynq需要下载sstate_arm_2021.1(5.5G),如果是zynqMP需要下载sstate_aarch64_2021.1(12.7G),另外还需要下载文件系统Downloads(42.7G);

b) 进入“Add pre-mirror url”,输入downloads的路径,注意格式

file://~/tools/01_petalinux/v2021/downloads;

c) 进入“Local sstate feeds settings”,设置sstate_arm路径

d) 使能离线编译(选中,按“y”),Enable Network sstate feeds可选可不选,如果下载的离线编译库不是最新的就选上,本地没有的可以自动从网上下载

5)保存,退出

6)petalinuxbsp.conf文件中声明离线编译路径

打开petalinux_from_bsp1/project-spec/meta-user/conf/petalinuxbsp.conf,新增如下变量

如果不在此声明的话会报错

7)修改boot.scr启动地址

在工程目录下,进入u-boot配置界面

petalinux-config –c u-boot

选择ARM architecture,并进入ARM architecture

找到Boot script offset,设置为0x1F10000,原因还是flash中的地址boot+bootenv+kernel=0x1F10000。

8)保存,退出

4. 编译petalinux工程

工程目录下,输入命令:petalinux-build

编译成功状态如下:

- bin文件打包

工程目录下,输入命令:petalinux-package --boot --fsbl ./images/linux/zynq_fsbl.elf --fpga ./images/linux/system.bit --u-boot,可生成BOOT.BIN

使用如下命令对生成的boot.bin、boot.scr、image.ub做“0”填充,为了匹配flash中的区域大小配置,注意填充的大小,最后一个boot.scr直接将flash剩余的地址全部做了填充

最后生成boot-all.bin,可直接下载到flash中,上电成功启动,本次测试flash大小为32MB。 文章来源:https://www.toymoban.com/news/detail-727635.html

文章来源:https://www.toymoban.com/news/detail-727635.html

但是网口驱动好像有问题,继续填坑……文章来源地址https://www.toymoban.com/news/detail-727635.html

到了这里,关于petalinux-2021.1在zynq7020的flash上启动linux的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!