名称:等精度频率计设计verilog quartus仿真

软件:Quartus

语言:Verilog

要求:

A:测量范围信号:方波

频率:100Hz~1MHz;

B:测试误差:<0.1%(全量程)

C:时钟频率:50kHz

D:预闸门时间:01s

E:系统时钟频率:50MHz

F:频率计算:保留1位小数

本代码下载:等精度频率计设计verilog,quartus仿真_Verilog/VHDL资源下载

FPGA代码下载网:hdlcode.com

部分代码展示

//运算锁存模块 module latch_buf( input clk_in,//输入50K基准时钟 input doors_open, input [31:0]CNT1_buf,//输出基准时钟计数器 input [31:0]CNT2_buf,//输出待测频率计数器 output [31:0]total_frequency//输出频率 ); reg [31:0] CNT1_bufc=32'd0;//基准时钟计数器寄存器 reg [31:0] CNT2_bufc=32'd0;//待测频率计数器寄存器 reg door_1s_buf=0; always@(posedge clk_in) door_1s_buf<=doors_open; wire door_1s_negedge; assign door_1s_negedge=~doors_open & door_1s_buf;//闸门信号下降沿 always@(posedge clk_in) if(door_1s_negedge==1)begin CNT1_bufc<=CNT1_buf;//基准频率计数 CNT2_bufc<=CNT2_buf;//待测频率计数 end //保留1位小数,即再乘以10 //待测频率计算=CNT2_buf*50000*10/CNT1_buf wire [63:0] mul_result; assign mul_result=CNT2_bufc*32'd500000; assign total_frequency=mul_result/CNT1_bufc;//单位0.1Hz endmodule

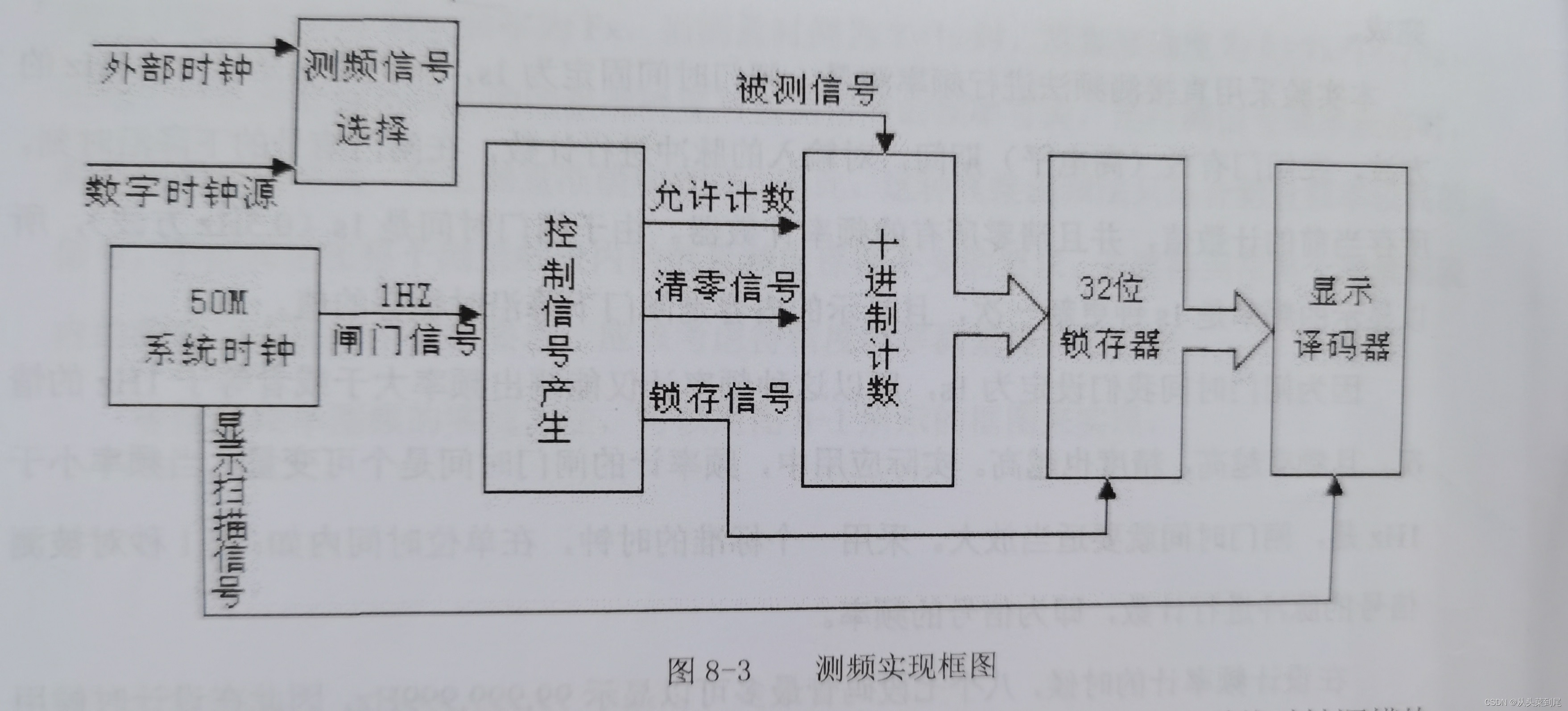

设计文档:

1. 工程文件

2. 程序文件

3. 程序编译

4. RTL图

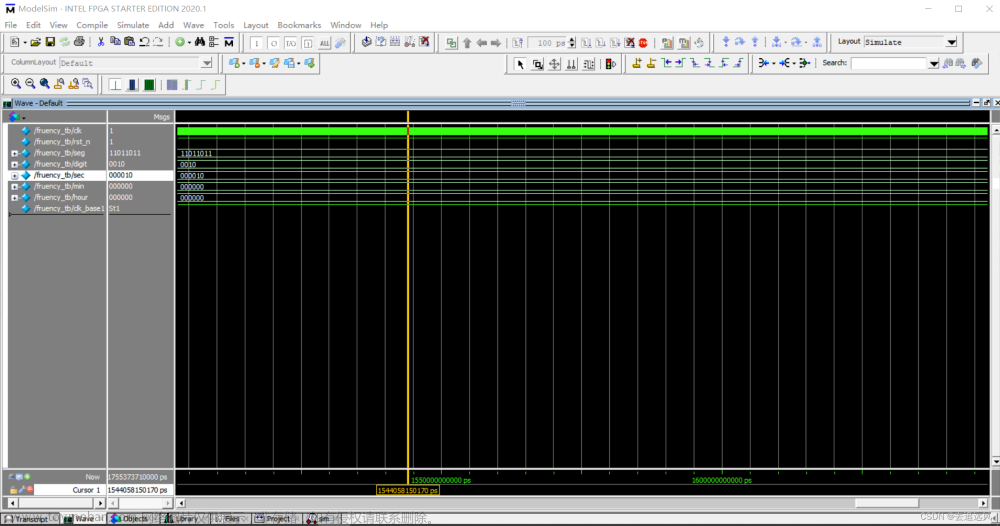

5. 仿真图

整体仿真图

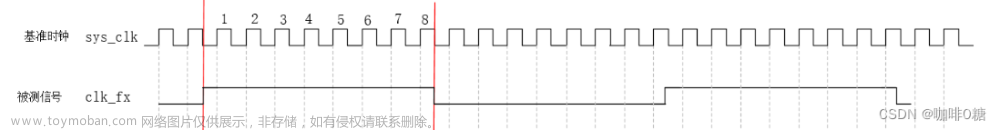

5.1 分频模块

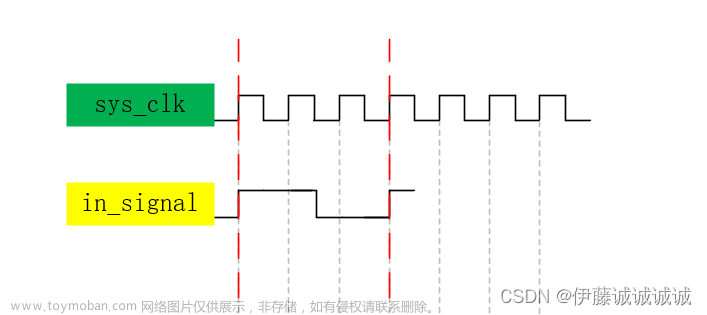

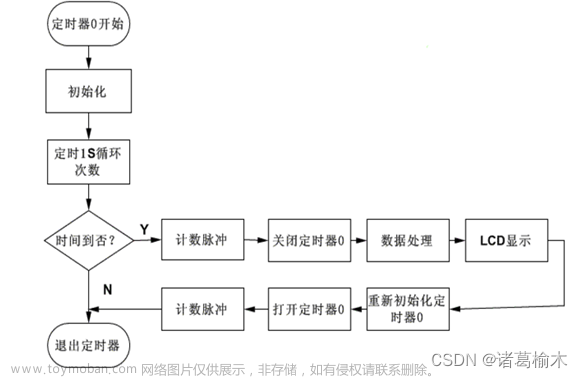

5.2 闸门信号产生模块

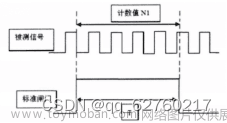

5.3 计数模块

5.4 运算锁存模块

5.5 数码管显示模块

文章来源:https://www.toymoban.com/news/detail-727815.html

文章来源:https://www.toymoban.com/news/detail-727815.html

设计文档.doc文章来源地址https://www.toymoban.com/news/detail-727815.html

到了这里,关于等精度频率计verilog,quartus仿真视频,原理图,代码的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!