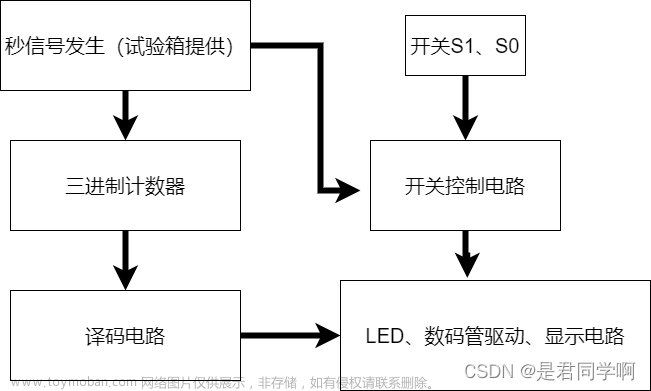

要求:用 Verilog HDL 以层次化的设计方法,结合实验 1(需修改部分代码), 使用下文计数器模块代码“Code-1 7 进制计数器”,将计数器输出 Q 与译码器输 入 x 相连,译码器输出 codeout 锁定到实验箱的 LED 上,设计一个彩灯控制器。 LED 在控制电路的驱动下,按图 2 所示规律点亮/熄灭(●表示亮灯,○表示灭 灯)。对整体电路进行仿真,应当能够看到 en 为高电平时计数器的输出值自动增 加,相应地译码器的输出依次变化,并循环。

真值表:

| en |

X0 |

X1 |

X2 |

Codeout0 |

Codeout1 |

Codeout2 |

Codeout3 |

Codeout4 |

Codeout5 |

| 0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| 1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| 1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

| 1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 | 1 |

| 1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 | 1 | 1 |

| 1 |

1 |

0 |

0 |

0 |

0 |

1 | 1 | 1 | 1 |

| 1 |

1 |

0 |

1 |

0 |

1 | 1 | 1 | 1 | 1 |

| 1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

module dingcengwenjian(clk,en,Q,codeout);//顶层文件 包含两个模块

input clk,en;

output [2:0]Q;

output [5:0]codeout;

comb_3(clk,en,Q);

comb_4(Q,seg,codeout);

endmodule module comb_3(clk,en,Q[2:0]);//这里一定要写分号!!!!

input clk,en; // 时钟信号输入

output [3:0] Q;// 计数器输出

reg [2:0] count; // 计数器寄存器

reg ret;

always @(posedge clk)

begin

if(en)begin

if (count == 3'b110) begin

count <= 3'b000; end// 计数器达到6时清零

else begin

count <= count + 1;end // 否则加一 非阻塞赋值,后面的语句可以接着进行

end

end

assign Q = (en)?count:3'b000; //组合逻辑 输出计数器值 阻塞赋值后面的不能进行

endmodule

module comb_4(X,seg,codeout);

input [2:0]X;

output seg;

output reg [5:0]codeout;

always@(*)

begin

case(X)//这里不需要冒号

3'b000:codeout<=6'b000000;

3'b001:codeout<=6'b000001;//这里需要非阻塞 左边是高位右边是低位

3'b010:codeout<=6'b000011;

3'b011:codeout<=6'b000111;

3'b100:codeout<=6'b001111;

3'b101:codeout<=6'b011111;

3'b110:codeout<=6'b111111;

default:codeout=6'bx;

endcase

end

endmodule 仿真波形图:

文章来源:https://www.toymoban.com/news/detail-728378.html

文章来源:https://www.toymoban.com/news/detail-728378.html

RTL图:

文章来源地址https://www.toymoban.com/news/detail-728378.html

文章来源地址https://www.toymoban.com/news/detail-728378.html

到了这里,关于【数电实验】汽车流动转向灯电路设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!