一种全加器的设计。

目录

一、全加器

二、代码实现

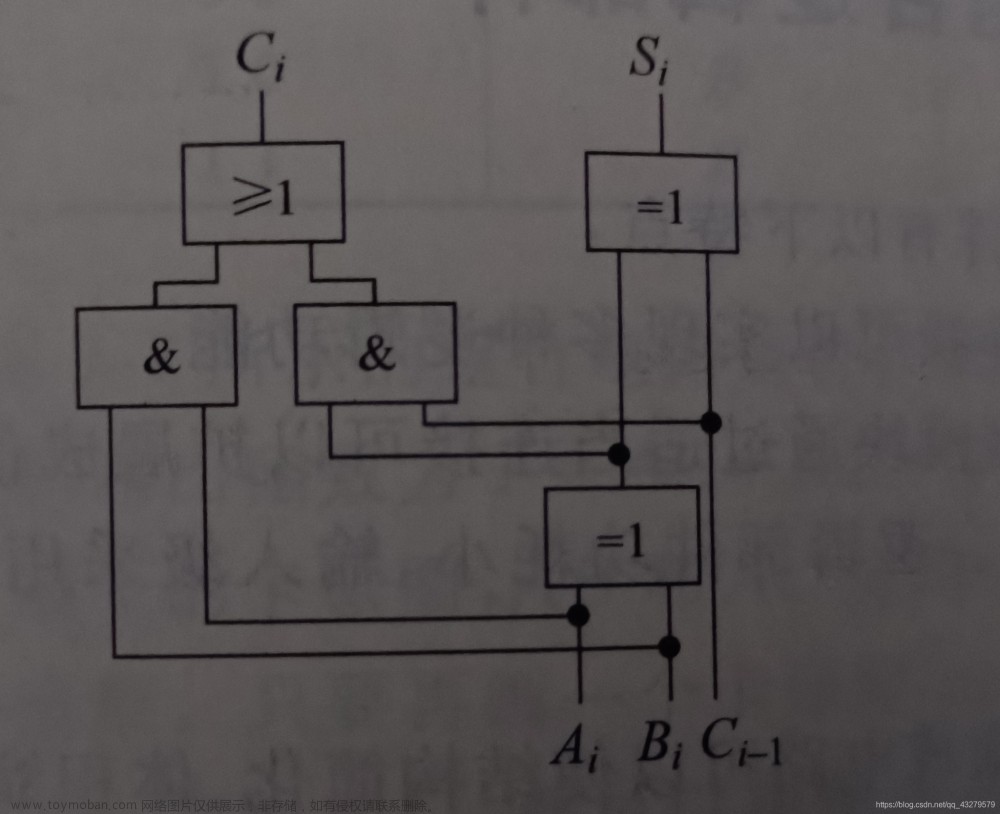

一、全加器

全加器是用门电路实现两个二进制数相加并求和的组合线路,也称为一位全加器,是一种常用的设计。全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器,例如常用的二进制四位全加器74LS283。

真值表:

| 输入 |

输出 |

|||

| C(i-1) |

Ai |

Bi |

Si |

Ci |

| 0 |

0 |

0 |

0 |

0 |

| 0 |

0 |

1 |

1 |

0 |

| 0 |

1 |

0 |

1 |

0 |

| 0 |

1 |

1 |

0 |

1 |

| 1 |

0 |

0 |

1 |

0 |

| 1 |

0 |

1 |

0 |

1 |

| 1 |

1 |

0 |

0 |

1 |

| 1 |

1 |

1 |

1 |

1 |

Ai和Bi为相加数,低位进位C(i-1),输出本位和为Si,向高位进位Ci。

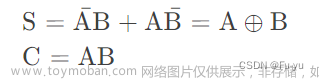

表达式:

Si = Ai⊕Bi⊕C(i-1)

Ci = Ai&Bi + C(i-1) & (Ai+Bi)

二、代码实现

上代码:

module full_adder #(parameter N=8)(

input clk,

input rst_n,

input [N-1:0]ain,

input [N-1:0]bin,

input cin,

output reg [N:0] sum

);

reg [N:0] c;

integer i;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

c <= 0;

sum <= 0;

end

end

always@(*)begin

c[0] = cin;

for(i=0;i<N;i=i+1)begin

sum[i] = ain[i] ^ bin[i] ^ c[i];

c[i+1] = (ain[i] & bin[i]) | (ain[i] & c[i]) | (bin[i] & c[i]);

end

sum[N] = c[N]; // 进位

end

endmodule总体使用了参数化设计。cin是接收到的进位,输出的sum最高位是本位的进位,与低位共同组成和。

测试波形:

文章来源:https://www.toymoban.com/news/detail-730728.html

文章来源:https://www.toymoban.com/news/detail-730728.html

为了更直观的观察,采用十进制显示。 文章来源地址https://www.toymoban.com/news/detail-730728.html

到了这里,关于Verilog设计_全加器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!