目录

1.边沿触发型触发器及其Verilog表述

2.电平触发型锁存器及其Verilog表述

3.含异步复位/时钟使能型触发器及其Verilog表述

4.同步复位型触发器及其Verilog表述

5.异步复位型锁存器及其Verilog表述

6.Verilog的时钟过程表述的特点和规律

7.异步时序模块的Verilog表述

8.4位二进制计数器及其Verilog表述

9.功能更全面的计数器设计

1.边沿触发型触发器及其Verilog表述

新语法:posedge

定义:对上升沿敏感的表述。

作用:告诉综合器构建边沿触发型时序元件。

与posedge对应的negedge,下降沿敏感表述。

凡是边沿触发性质的时序元件必须在敏感信号表中使用边沿敏感表述,而不用此表述产生的时序电路都是电平敏感时序电路。

2.电平触发型锁存器及其Verilog表述

当CLK为高电平时,Q随着D的变化而更新,当CLK为低电平时,将保存其在高电平时锁入的数据。

工作原理: 时钟上升沿到来时,将D送入Q,属于边沿触发,敏感信号表中posedge表述。

当CLK=1,Q随着D的变化而更新,当CLK=0时, Q值保持,属于电平触发,敏感信号表列电平信号。

3.含异步复位/时钟使能型触发器及其Verilog表述

异步:独立于时钟控制的复位控制端RST,在任意时刻,只要RST=0,D触发器的输出端即刻被清零,与时钟的状态无关。EN的功能是,只有当EN=1时,时钟上升沿才有效。

module DFF2(RST,CLK,EN,D,Q);

input RST,CLK,EN,D;

output Q;

reg Q;

always@(posedge CLK or negedge RST)begin

if(!RST)

Q<=0;

else if(EN)

Q<=D;

end

endmodule

复位信号RST=0时,不管时钟信号是何种状态,Q即刻被清0。

4.同步复位型触发器及其Verilog表述

同步:指RST信号只有在时钟信号有效时,才能起作用。

module DFF3(RST,CLK,D,Q);

input RST,CLK,D;

output Q;

reg Q;

always@(posedge CLK)begin

if(RST==1)

Q<=0;

else

Q<=D;

end

endmodule 复位信号RST=1时,且时钟上升沿到来,才对Q清0;反之复位信号RST=1时,时钟上升沿没有到来,则Q不能被清0。

复位信号RST=1时,且时钟上升沿到来,才对Q清0;反之复位信号RST=1时,时钟上升沿没有到来,则Q不能被清0。

5.异步复位型锁存器及其Verilog表述

异步复位:RST独立于时钟的状态;

锁存器:属电平敏感型电路,类似组合逻辑电路描述法。 RST=0时,不管CLK是何种状态,Q即刻被清0。

RST=0时,不管CLK是何种状态,Q即刻被清0。

RST=1时,CLK=1时,Q随D的变化而变化,CLK=0时,Q保持CLK=1时的值。

6.Verilog的时钟过程表述的特点和规律

1)敏感信号表含有negedge和posedge时,选择性地改变敏感信号的放置是可以影响综合结果的,例如,同步复位型触发器和异步复位型触发器;

2)敏感信号表中一旦含有negedge或posedge的边沿敏感信号后,所有其他电平敏感型信号都不能放在敏感信号表中;

3)如果在同一模块中含有独立于主时钟的时序或组合逻辑,必须在另一过程描述。

对于边沿触发型时序电路,遵循以下规律:

1)如果将信号定义为边沿敏感信号,则必须在敏感信号表中用negedge或posedge给出表述, 但在always@过程结构中不能再出现该信号了,例如,时钟触发器时钟CLK。

2)如果一个对应于时钟的电平敏感的异步控制信号,则除了在敏感信号表中给出对应的表述外,在always@过程结构中必须明示这一信号的逻辑功能,如异步RST。

3)如果一个信号是对应于时钟的同步控制信号,则不允许在敏感信号表中出现,如同步RST。

4)敏感信号分为两种类型:电平敏感信号和边沿敏感信号,在同一过程的敏感信号表中,只能放置一种敏感信号,不能混放。

7.异步时序模块的Verilog表述

module AMOD(D,A,CLK,Q);

input D,A,CLK; output Q;

reg Q,Q1;

always@(posedge CLK)begin

Q1=~(A|Q);

end

always@(posedge Q1)begin

Q=D;

end

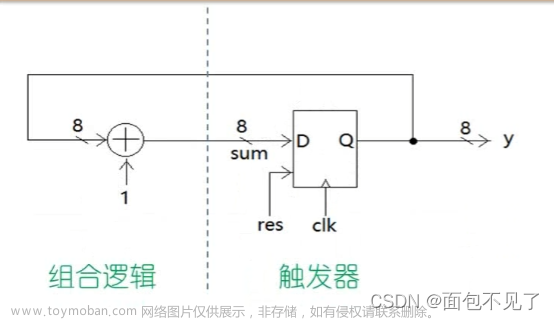

endmodule8.4位二进制计数器及其Verilog表述

分析:最简单的4位二进制计数器应该有一个时钟输入CLK,4位二进制的计数值输出Q[3:0],每进入一个时钟,输出数据Q将增加1,随着时钟CLK的不断出现,计数值Q从0000至1111循环输出值。

module CNT4(CLK,Q);

input CLK;

output [3:0] Q;

reg [3:0]Q1;

always@(posedge CLK)

begin

Q1<=Q+1;

end

assign Q=Q1;

endmodule

9.功能更全面的计数器设计

带有异步复位、同步使能和预置型十进制计数器。

输入输出分析:

输入信号包括时钟信号CLK、异步复位信号RST,同步使能信号EN,同步预置信号LOAD,预置数DATA[3:0]。

输出信号包括计数输出DOUT[3:0],计数溢出时的进位信号COUT。

逻辑功能分析:

1)异步复位:任意时刻,只要RST为0,计数器都有清0;

2)当RST=1、使能EN=1,且CLK上升沿到来时,当LOAD=0将DATA预置给计数输出值;LOAD为1时,计数器正常计数,当计数值为9时,COUT输出进位值1。

文章来源:https://www.toymoban.com/news/detail-732636.html

文章来源地址https://www.toymoban.com/news/detail-732636.html

到了这里,关于【FPGA】Verilog设计入门——时序模块及其Verilog表述的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!