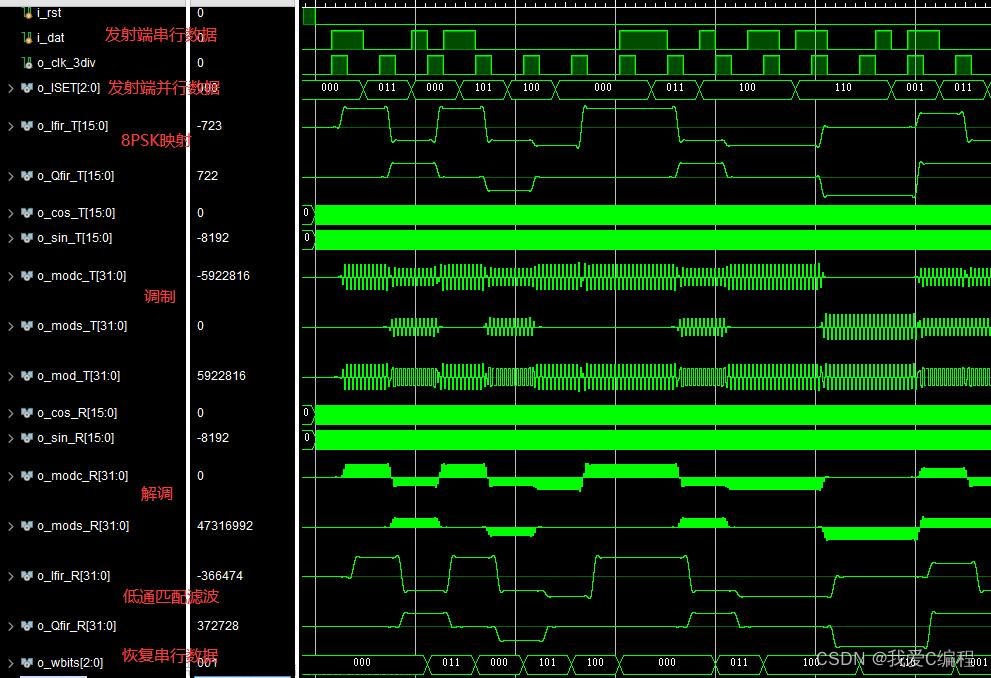

FPGA数字调制系统中的自动增益控制(AGC)详解

在数字通信系统中,常常需要将原始信号进行数字调制以便于传输。而在数字调制系统中,自动增益控制(Automatic Gain Control,AGC)是一个十分重要的模块。本文将深入探讨FPGA数字调制系统中的AGC实现方案。文章来源:https://www.toymoban.com/news/detail-734693.html

AGC旨在使接收到的信号的幅度保持在一个合适的范围内,以保证其能够被后续模块正常处理。在FPGA中,我们可以通过一些简单的代码实现AGC模块。下面是一个基于Verilog HDL语言的示例代码:文章来源地址https://www.toymoban.com/news/detail-734693.html

module AGC (

input clk, // 时钟信号

input rst, // 复位信号

input signed [15:0] indata, // 输入信号

output signed [15:0] outdata // 输出信号

);

reg signed [15:0] gain = 16'd32768; // 初始增益值

reg signed [15:0] max_data = 16'd0; // 最大值

reg signed [15:0] min_data = 16'd0; // 最小值

always @(posedge clk, posedge rst) begin

if (rst) begin

gain <= 16'd32768;

max_data <= 16'd0;

min_data <= 16'd0;

outdata <= 16'd0;

end

else begin

max_data <= (indata > max_data) ? indata : max_data;

min_data <= (ind到了这里,关于FPGA数字调制系统中的自动增益控制(AGC)详解的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!