举重比赛有三名裁判,当运动员将杠铃举起后,须有两名或两名以上裁判认可,方可判定试举成功,若用A、B、C分别代表三名裁判的意见输入,同意为1,否定为0;F为裁判结果输出,试举成功时F=1,试举失败时F=0。

一、分析与Verilog代码

真值表:

| A | B | C | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

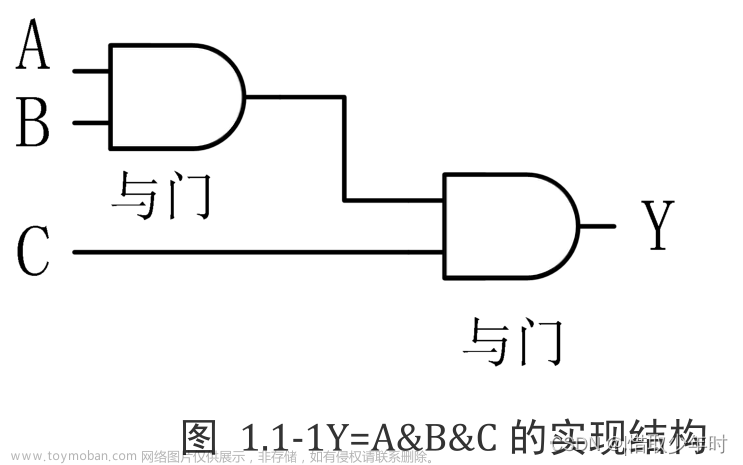

因而可以得到 F = (A&&B) || (A&&C) ||(B&&C)

Verilog代码:

module test(

input wire A,

input wire B,

input wire C,

output wire F);

reg result=0;

always @(A,B,C)

result = (A&&B) || (A&&C) ||(B&&C);

assign F = result;

endmodule

二、软件仿真

tb文件:

module test_tb();

wire result;

reg [3:0] count;

reg A, B, C;

reg clk;

always #5 clk=~clk;

initial begin

clk<=0;

A<=0;

B<=1;

C<=1;

count<=1'b0;

end

always @ (posedge clk) begin

if (count == 4'd2) begin

A<=~A;

end

else if(count ==4'd4)begin

B<=~B;

end

else begin

C=~C;

end

if (count==4'd4)begin

count<=4'b0;

end

else begin

count<=count+1'b1;

end

end

test u_test(

.A (A),

.B (B),

.C (C),

.F (result)

);

endmodule

仿真结果:

当同一时刻,A、B、C中有大于等于两个为高电平时,输出为高电平。

三、硬件箱实现

裁判A、B、C通过按键K1、K2、K3输入自己的结果,若通过,则绿色的LED灯L2亮起;若不通过,LED不亮。

1、代码调整

由于led是低电平驱动,所以需要对代码的最后做一点小的修改:

assign F = result;

↓ ↓ ↓

assign F = !result;

整体代码如下:

module test(

input wire A,

input wire B,

input wire C,

output wire F);

reg result=0;

always @(A,B,C)

result = (A&&B) || (A&&C) ||(B&&C);

assign F = result;

endmodule

2、实现

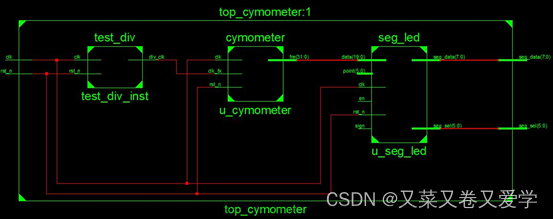

编译没有问题后可以查看一下RTL图:

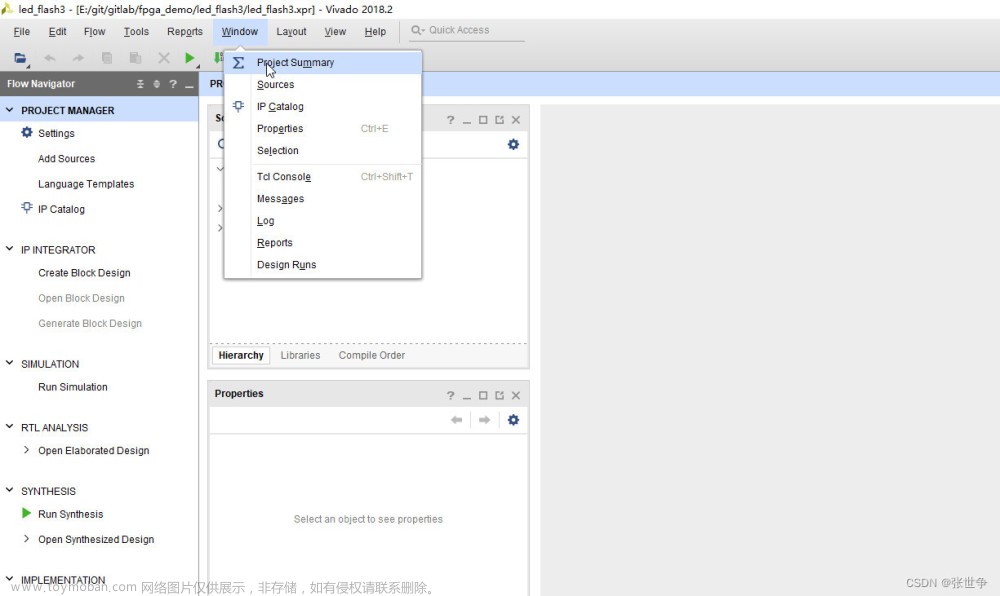

接着进行引脚分配,引脚分配结果如下:

分配完引脚之后再编译一次,接着进行sof文件的烧录。

用下载线将按键接口JX22连接到JP5,将按键接口JX5连接到JP1,JTAG接口用下载线连接到电脑的USB口。

(为什么要这样接线可以参考《【FPGA实验2】二进制转为格雷码》中的【三、实验箱实验】➡️【3、引脚分配】。)

4、实验结果

【FPGA实验1.5】举重裁判机制文章来源:https://www.toymoban.com/news/detail-734825.html

Foever young,always tearful. 😏文章来源地址https://www.toymoban.com/news/detail-734825.html

到了这里,关于【FPGA实验4】举重比赛机制的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!