一、组合电路设计的一般步骤:

逻辑抽象=>列出真值表=>逻辑表达式=>逻辑电路图

Notes:

a、可以先对逻辑表达式进行化简得到最简与或式、最简或与式、与非、或非,再对电路进行建模,从而提高电路的运行效率和可读性;

b、最基本的逻辑化简公式有很多,最有效的也是最基本的比如反演和对偶;

c、异或和同或的关系也很重要;

二、 电路的基本组成:

1、存储电路:保存电路当前的状态;(如触发器、锁存器等)

2、组合逻辑电路:电路的输出仅与当前的输入有关;

3、时序逻辑电路:电路任一时刻的输出不仅取决于当前的输入,而且与电路原来的状态相关;

由图可见:时序逻辑电路是包含组合逻辑电路的,本质上都是元器件的组合。

三、锁存器:构成时序逻辑电路的基本部件,是电平触发且输出跟随输入变化。

1、基本双稳态电路:能够长期保存某种逻辑状态的电路

在双稳态电路中,存储的逻辑状态是随机的,并且无法改变和控制工作状态,有很大的局限性。

2、用或非门组成的SR锁存器:

(1)电路原理和结构:

Notes:当SR从00变到11时,输出Q的波形是不确定的,因为不确定该保持什么状态。

(2)动态特性分析:(用于某些时序逻辑电路的时序分析)

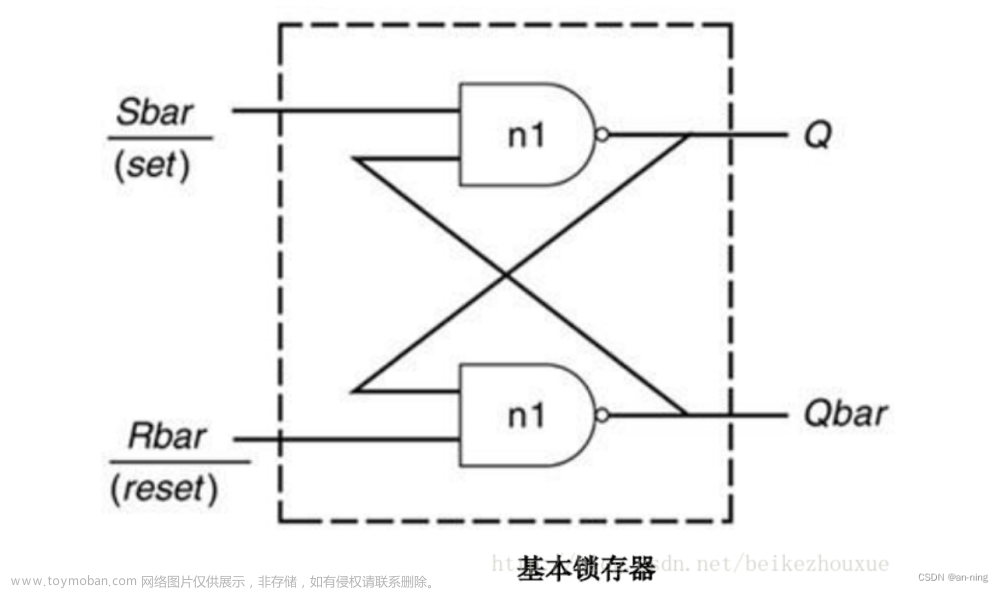

3、用与非门组成的SR锁存器:

(1)电路结构与原理:

(2) 应用:去抖动电路

4、门控SR锁存器:

(1)电路结构与原理:

Notes:a、当E=0时,锁存器被禁止;

b、当E=1时,接收输入信号;

c、禁止输入S=R=1;

5、D锁存器:

(1)分类:逻辑门控D锁存器、传输门控D锁存器;

(2)逻辑门控D锁存器:

Notes:a、E=0,保持;

b、E=1,Q=D;

c、D锁存器有两个稳定状态,如果输入满足一定的条件,输出就会发生翻转;

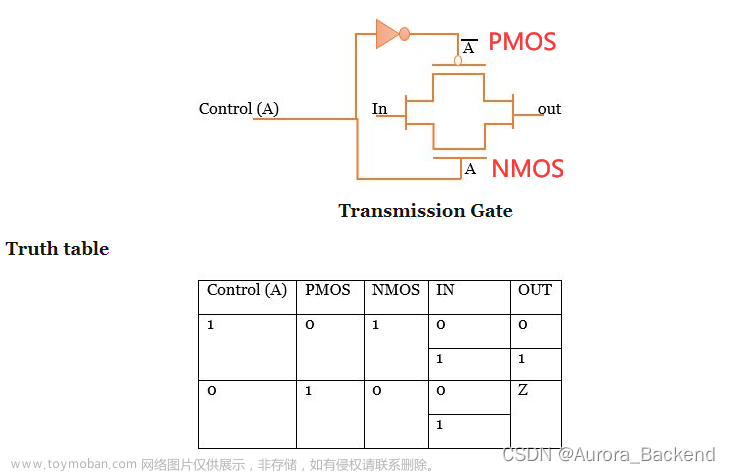

(3)传输门控D锁存器:由基本双稳态电路和传输门组成

Notes:a、A和B导通的电平条件是上低下高;

b、同一逻辑功能可以用不同的电路实现;

(4)典型D锁存器集成电路:74HC/HCT373

(5)D锁存器的动态特性:未完待续,会结合FPGA的时序分析来讲解。

四、触发器:状态只在CP信号的上升沿或者下降沿更新,属于是边沿触发。

1、分类:

(1)按照逻辑功能分类:SR触发器、JK触发器、D触发器、T触发器

(2)按照电路结构分类:主从触发器、维持阻塞触发器、利用传输延迟的触发器

2、主从D触发器:

(1)电路结构与原理:

Notes:a、CP=0时,则Em=1,Es=0;Qm跟随输入D变化,使Qm=D。从锁存器维持原状不变;

b、CP由0跳变到1时,则Em=0,Es=1;

(2)例题:

(3)有其他控制端的D触发器:异步输入端(直接置1端/异步置1端、直接置0端/异步清零端/异步复位端)

Notes:a、如果CP没有上升沿的话,触发器的输出只取决于S和R的输入;

b、如果CP有上升沿的话,触发器的输出和D相同;

(4)应用:

(5)有使能端的D触发器

(6)主从D触发器的动态特性:FPGA的时序分析

3、维持阻塞D触发器:在TTL集成电路中,常常使用维持阻塞结构形式。是在3个电平触发的SR锁存器上改进得到。

(1)电路的结构与原理:

Notes:a、上升沿触发

(2)有异步输入端的维持阻塞D触发器:

Notes:a、由于直接置1和清零和CP信号无关,所以称置1、清零操作是异步的;

b、上下为10时Q输出为0,上下当为01时Q输出1;

五、触发器的逻辑功能:特性表、特性方程、状态图、时序波形图等

1、D触发器:

2、JK触发器:

(1)电路的原理和结构:

(2)用D触发器构成JK触发器:

3、T触发器:

(1)电路原理与结构:

(2)用D触发器构成T触发器:

4、T ’ 触发器:

(1)电路结构与原理:

(2)用D触发器构成T ’触发器:

5、SR触发器:

(1)电路结构与原理:

文章来源:https://www.toymoban.com/news/detail-736649.html

文章来源地址https://www.toymoban.com/news/detail-736649.html

到了这里,关于数字电子技术之锁存器和触发器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!